时间:2025-04-08 来源:网络收集 关于我们 0

1 配置模式

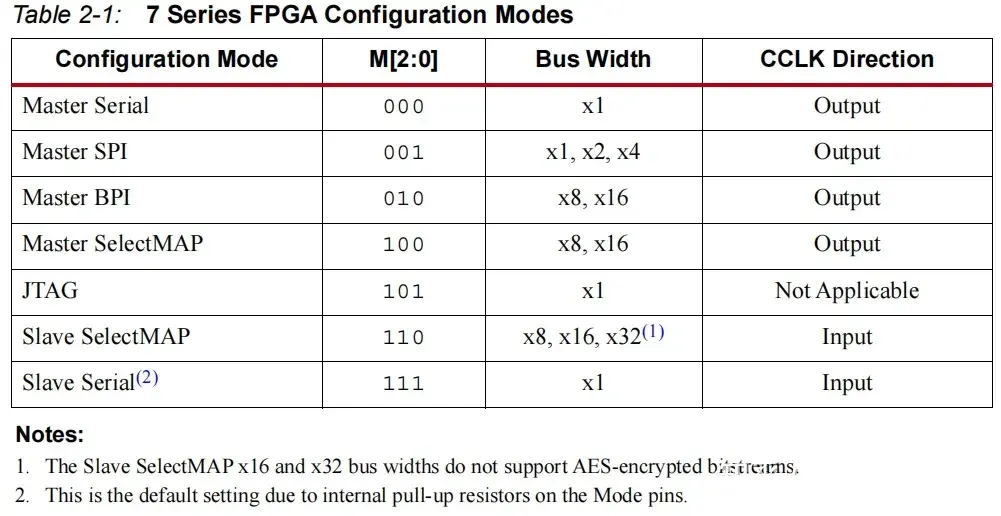

由于Xilinx FPGA配置数据存储在CMOS配置锁存器(CCL)中,因此必须在断电后重新配置。比特流每次都通过特定的配置引脚加载到器件中。常用的配置模式可以分为:

主模式:主串口、主SelectMAP(并行×8 ×16)、主SPI(×1 ×2 ×4)、主BPI(×8 ×16

从模式:从串口、从SeletMAP(并行×8 ×16 ×32)J

TAG模式(调试模式)

系统模式(多片配置模式)

通过在专用模式输入引脚M[2:0]上设置适当的电平来选择特定的配置模式。M2、M1和M0模式引脚应通过上拉或下拉电阻(≤1kΩ)或直接接地或VCCO_0设置为恒定直流电压电平。在配置期间和配置之后不应切换模式引脚。

无论模式引脚M[2:0]设置如何,JTAG/边界扫描配置接口始终可用。

主模式和从模式指的是配置时钟CCLK的方向,在主模式中CCLK为输出,从模式中CCLK为输入。

由于CCLK引脚存在容差,因此可以使用比CCLK更精准的时钟EMCCLK引脚。启用外部主配置时钟(EMCCLK)选项,全速加载配置程序,具体见UG470 2章节。

1.1.1 主模式

FPGA自加载配置模式,通常称为主模式,可用于串行或并行数据路径。主模式利用各种类型的非易失性存储器(如Flash、EEPROM等)来存储FPGA的配置信息。FPGA在驱动配置逻辑的内部振荡器中生成配置时钟信号,并在CCLK输出引脚上可见。

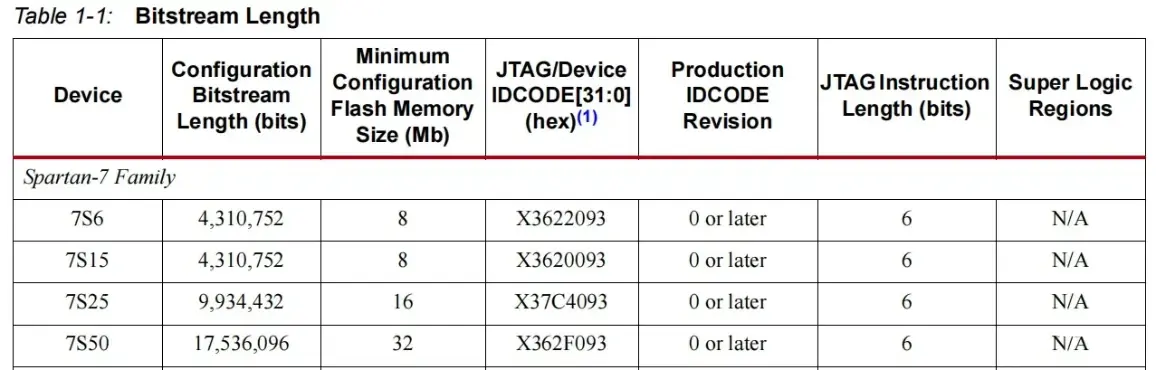

【UG470】的表1-1提供了7系列生成比特流长度,可以注意到不同型号的FPGA所需的最小配置Flash容量不同:

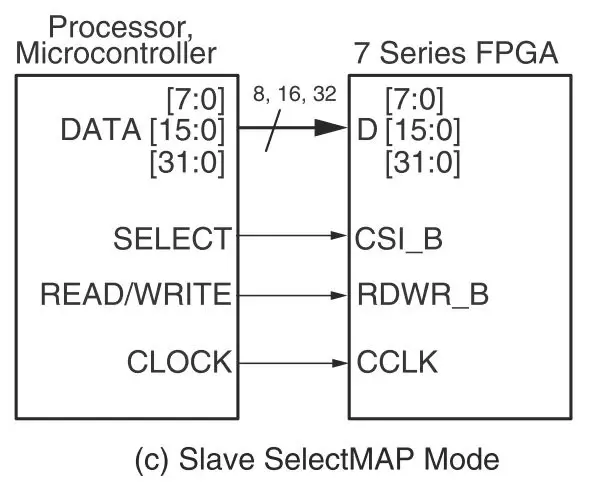

1.1.2 从模式

外部控制加载FPGA配置模式,通常称为从模式,也可用于串行或并行数据路径。在从模式下,处理器、微控制器、DSP处理器或测试仪等外部“智能代理”将配置映像下载到FPGA中,从配置模式的优势在于FPGA比特流几乎可以驻留在整个系统中的任何位置。

1.2 7种配置模式

1.2.1 主串配置模式

在该模式下,FPGA向外部的非易失性串行数据存储器或者控制器发出CCLK时钟信号,配置数据会以串行方式载入FPGA,在前几代的FPGA中,存储器通常选择Xilinx官方的XCF串行系列存储器,并给出了相应的设计原理图,但在7系列FPGA中,这种方式被放弃了,其官方的配置文档里并无主串配置模式的相关详细描述。

1.2.2 从串配置模式

如下图1所示,在该模式下,由外部的处理器提供CCLK时钟和串行数据,用户实现起来相对复杂,不够大众化,不做介绍。

1.2.3 主并配置模式

官方文档并无详细设计描述,无从参考。

1.2.4 从并配置模式

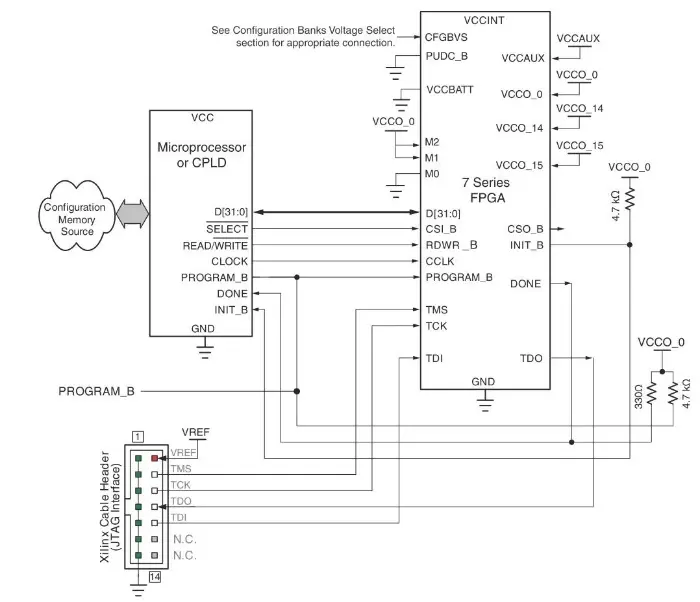

如下图所示,在该模式下,外部处理器提供配置时钟和并行的配置数据,该模式相对于串行方式来说,配置的速度快,但设计稍微复杂。下图为官方给出的详细配置原理图,该模式同样使用较少。

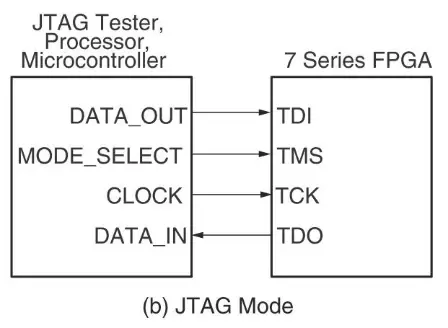

1.2.5 JTAG配置模式

如下图所示,该模式属于工程调试模式,咱们在设计FPGA时必带这种模式。该模式只能在线配置和调试FPGA,无法存储逻辑代码。最简单的操作方式是使用Xilinx官方提供的专用JTAG调试下载器,但同时也允许用户通过外部处理器自行设计JTAG的数据协议来配置FPGA逻辑代码。再次强调,该模式只是一个调试模式。

1.2.6 主SPI配置模式

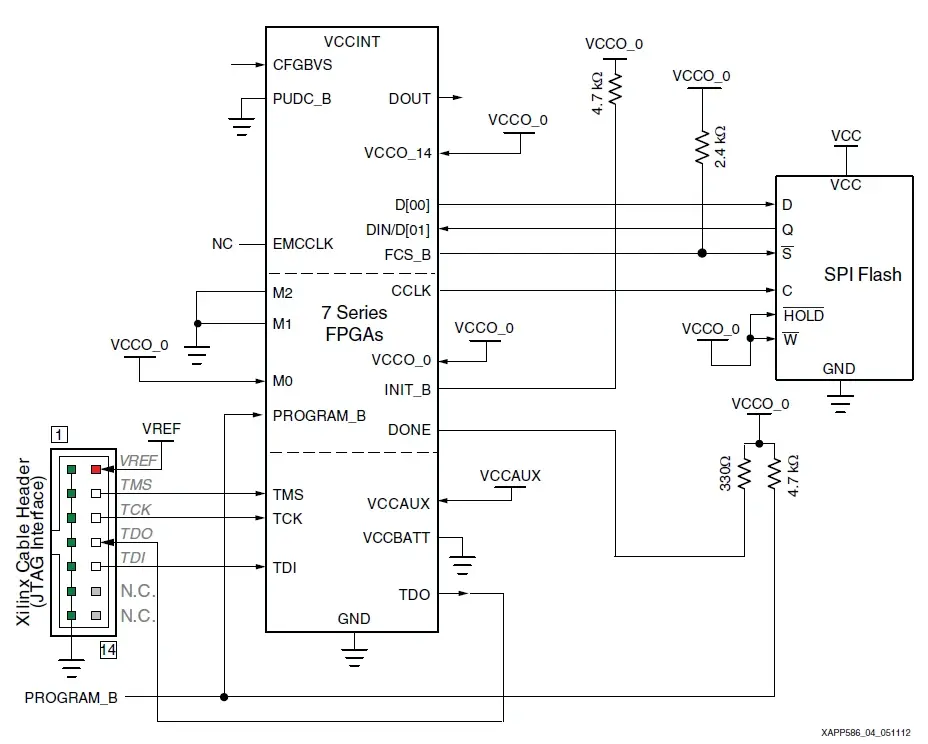

这种模式应该算是咱们使用最广泛的配置模式了,通过外挂一个SPI存储器即可。通常该模式和JTAG配置模式一起设计。JTAG模式在线调试好逻辑代码后,将该逻辑代码存储在SPI存储器中,以后FPGA上电后就会自动载入存储器中的逻辑代码。下图为官方给出的详细配置原理图。

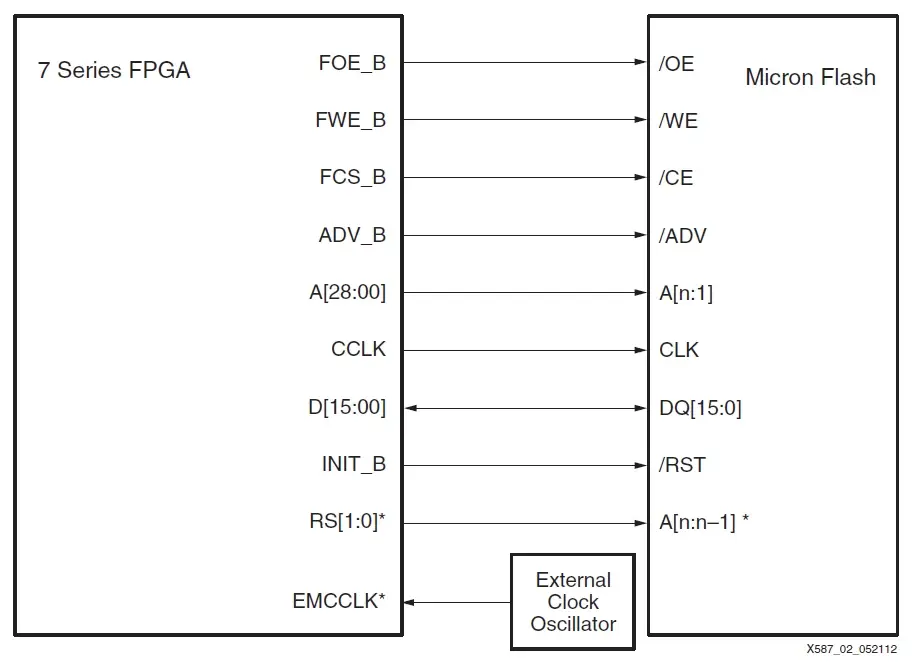

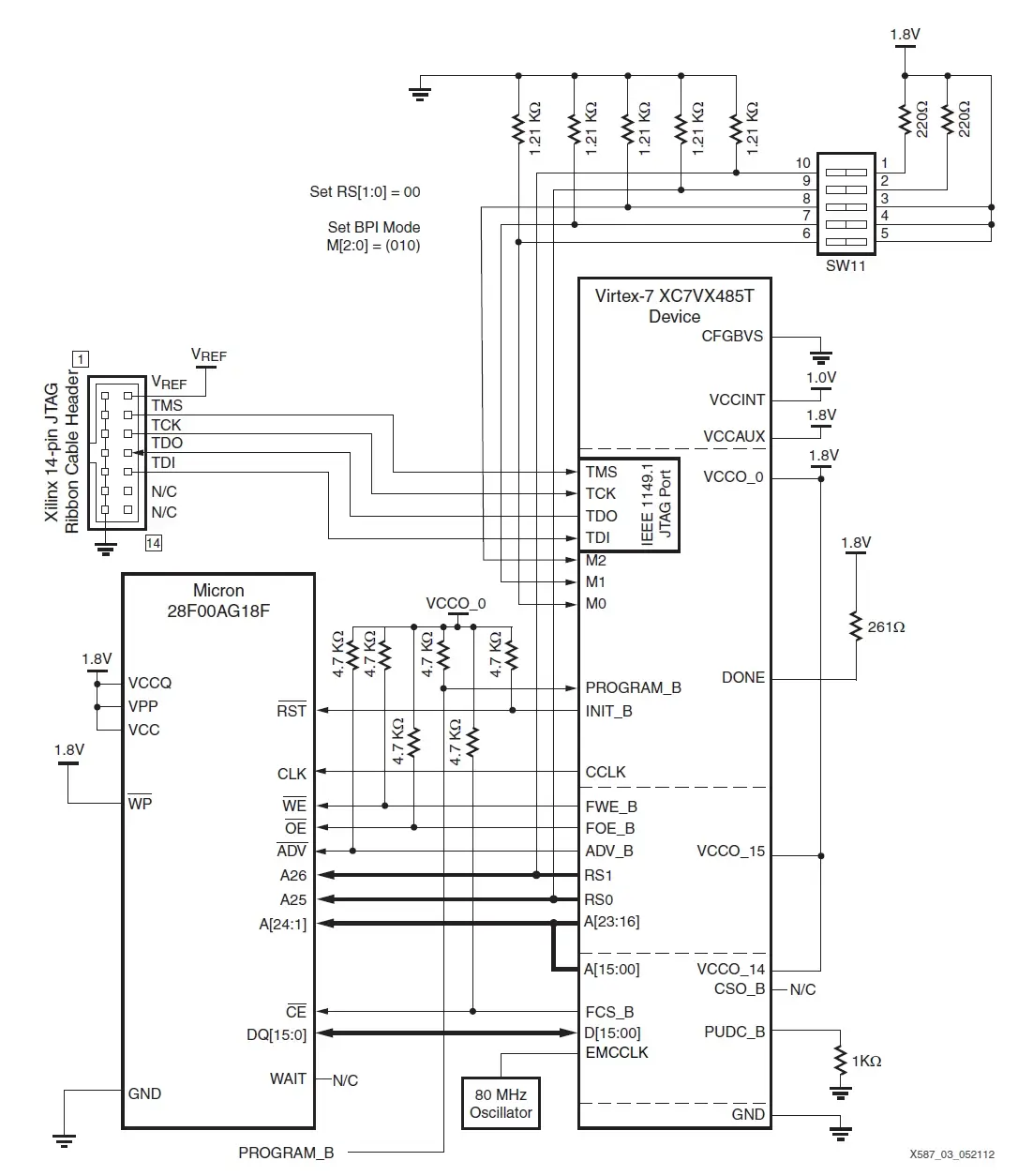

1.2.7 主BPI配置模式

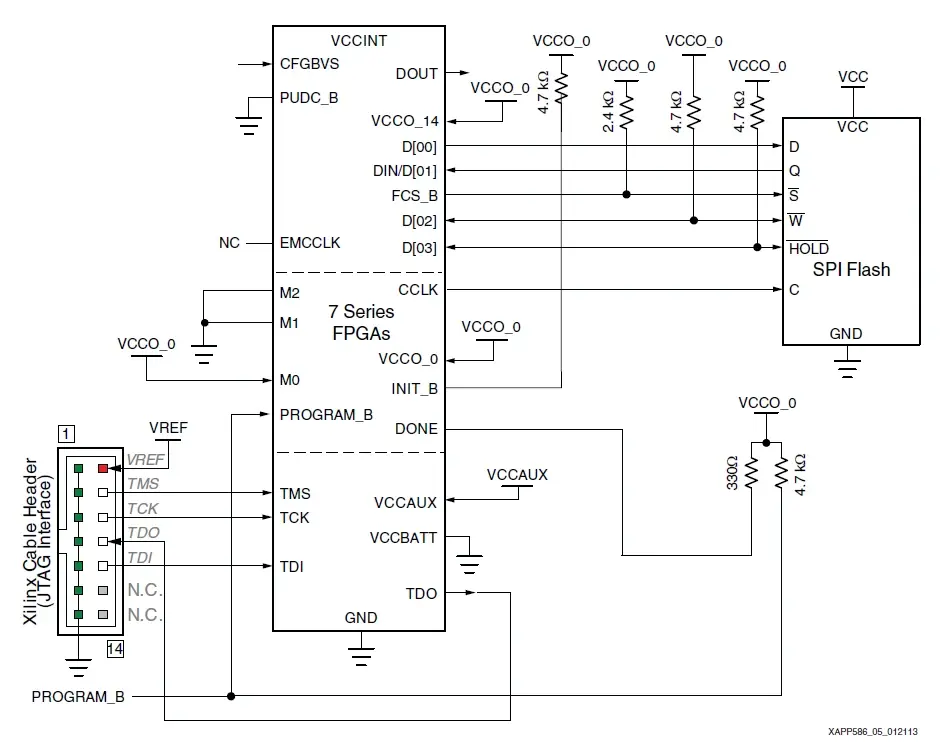

该模式的时钟CCLK同样由FPGA提供,并行的数据比SPI模式的串行数据配置速度要快,但设计稍微复杂一点。下图为官方给出的详细配置原理图:

我们在设计FPGA时,基本上都是采用JTAG配置模式+主SPI配置模式或者JTAG配置模式+主BPI配置模式。前者用于一般的应用,后者用于对FPGA上电后逻辑代码载入速度有较高要求的应用。

1.2.8 FPGA BPI加载时间(参考xapp587)

并行NOR FLASH是存储和传输比特流的常用选择,因为×16的数据总线可提供比SPI FLASH更快的配置,此外,NOR FLASH还可提供更大的容量。

BPI配置接口

CCLK:该引脚是除JTAG之外的所有配置模式的初始配置时钟源。同步读取模式下CCLK必须与BPI FLASH相连接以便顺序输出数据;异步读取模式下CCLK悬空,不直接为BPI FLASH提供时钟,由FPGA内部使用来生成地址和采样数据。

EMCCLK:该引脚为外部主配置时钟输入。此输入提供外部时钟,FPGA配置控制器在从比特流标头读取EMCCLK命令后切换使用此时钟而不是CCLK(内部配置时钟)。EMCCLK可实现更可预测的配置时间,因为时钟容差由所选的外部振荡器决定。(与SPI FLASH相同)

RS[1:0]:预留引脚。用于多bit程序,以在多版本之间进行选择并提供回退功能。当检测到配置错误时,RS [1:0]被主动为低以加载回退bit文件。

2、BPI FLASH配置实例

下图中EMCCLK外部输入80MHz时钟,RS引脚为预留引脚,如不需要修订程序则悬空处理。

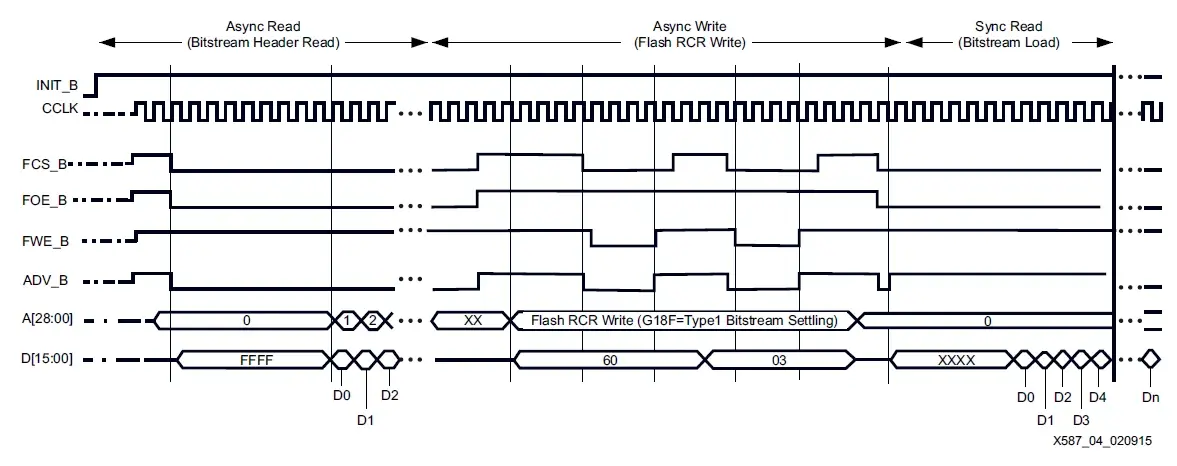

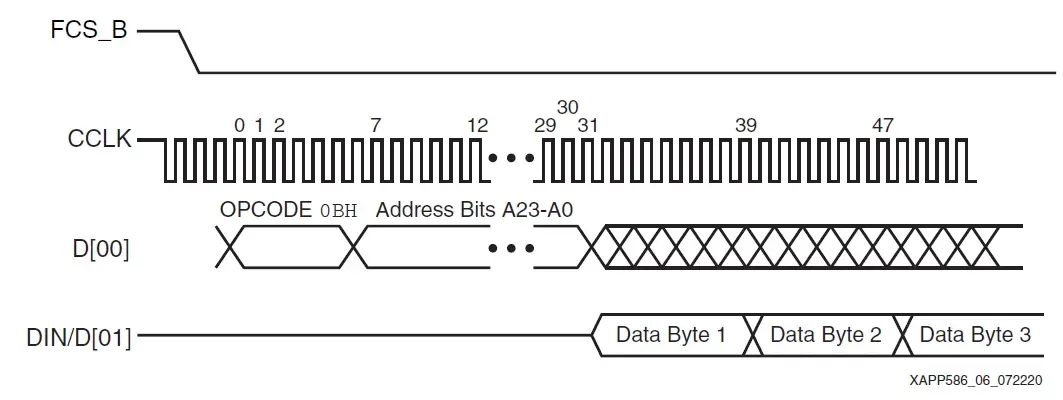

3、BPI FLASH配置时序

在BPI配置模式下,FPGA始终以异步读取模式从NOR flash开始读取。即从给定的起始地址递增地址总线,NOR flash发送回比特流数据。

当在比特流头中读取同步命令时,FPGA配置控制器对连接的BPI FLASH的读配置寄存器(RCR)执行异步写操作以设置同步模式和延迟位。

在成功写入RCR之后,FPGA控制器然后启动同步读取并读取比特流数据内容。配置完成后,保持同步读取模式。

BPI配置时序波形图

4、配置时钟最大频率计算

要计算传输的最大频率需要考虑到BPI FLASH输出时钟规范(BPI datasheet)及电路的延迟。公式如下:

TCHQV(Flash clock to out):BPI FLASH手册中有明确说明该时钟的输出数值。如PC28F00AP30TF,其TCHQV为17ns,如下图:

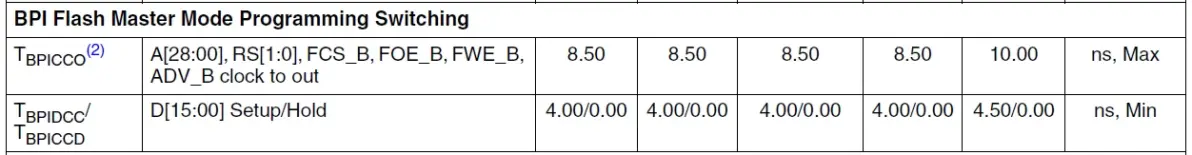

TBPIDCC(FPGA data setup):FPGA手册中有明确说明数据配置时间,如XC7K325T,其TBPIDCC为4ns,如下图:

Tbd(Board delay):经验值每英寸165ps。

假设Tbd为0.2ns,则最大频率=1/((17+4+0.2)ns) = 47MHz,最大频率为47MHz,实际选择需要考虑到CCLK的容错按照±50%,CCLK1.5应小于47MHz。

5、同步及异步读取模式下的配置时间

配置时间=bit文件大小/(最大频率数位宽据)

简单来说,将CCLK引脚接至FPGA并使用该时钟进行数据读取时为异步读取模式,其CCLK采用典型值6MHz,对于大小为162,187,488 Bits的bit文件来说,其配置时间则为:162,187,488Bit/(6M16)=1.689s,一般来说,CCLK可以修改为12MHz,从而加快程序下载速度。

使用外部EMCCLK时钟为同步读取模式,若外部使用40MHz的时钟,则配置时间为(使用EMCCLK时钟时则不需要考虑时钟的容错):162,187,488Bit/(40M16)=253ms

6、软件配置

在ConfigRate选项中可配置速率:

1.2.9 FPGA SPI加载时间(参考xapp586)

SPI Flash ×1/×2配置实例

SPI Flash ×4配置实例

SPI FLASH配置注意事项

上电加载过程中,FPGA和SPI Flash都要进行自检,自检完成后FPGA将读命令发送到SPI Flash以检索配置数据,此时SPI Flash必须准备好响应此命令。通常,FPGA的自检时间(毫秒级)要长于SPI FLASH的自检时间(微秒级)。

SPI FLASH配置时间

在7系列FPGA中,内部振荡器(FMCCKTOL)的频率容差很大,减小配置时间至关重要,建议使用外部时钟(EMCCLK)。

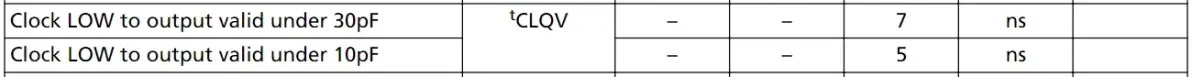

TSPITCO(SPI FLASH输出时钟):根据SPI FLASH数据手册,SPI FLASH时钟输出具有多个值,具体取决于VCC和输出引脚上的电容。这里以N25Q128A13为例手册中对于时钟的频率范围如下图:

其范围为5到7ns之间。

Tspiddc(FPGA data setup):Kintex-7 FPGA及Artix-7 FPGA的配置时间为3.0ns。

Ttpd(CCLK到C引脚延时时间):经验是每英寸165ps,为了获得更准确的结果,建议使用仿真。

在确定最佳配置速率后,设计人员需要将总比特流大小除以配置速率,以确定×1模式下的总配置时间。如果使用×2或×4数据宽度,则除以宽度。

最大配置时钟频率 = 1/(7ns+3ns+2ns)=83.3MHz,设计人员应考虑使用FPGA的内部振荡器,最接近83.3 MHz的值为66 MHz。但是,XC7K325T的频率容差(fMCCKTOL)为±50%,因此该时钟频率可能为(66 MHz x 1.5)= 99 MHz,超出了理论计算值。

下一个最快的配置速率是50 MHz,其最大频率为(50 MHz x 1.5)= 75 MHz。满足要求小于83.3MHz。

假设BIT流文件大小为91,548,896 bits(约为11MB文件),FPGA在1X模式及50MHz的配置速率下,其配置时间为 91,548,896 bits/50MHz = 1.83s

假设配置速率为80 MHz,其配置时间为 91,548,896 bits/80MHz = 1.144s,在此基础上如果为4X模式,其配置时间为 91,548,896 bits/80MHz/4 = 286ms

5、软件配置

黑色字体为默认配置,从菜单栏上的Process下拉菜单中选择Process Properties,然后选择Configuration Options,从窗口底部的“属性”显示级别下拉菜单中,选择“高级”以查看所有选项。

1.3 端口配置

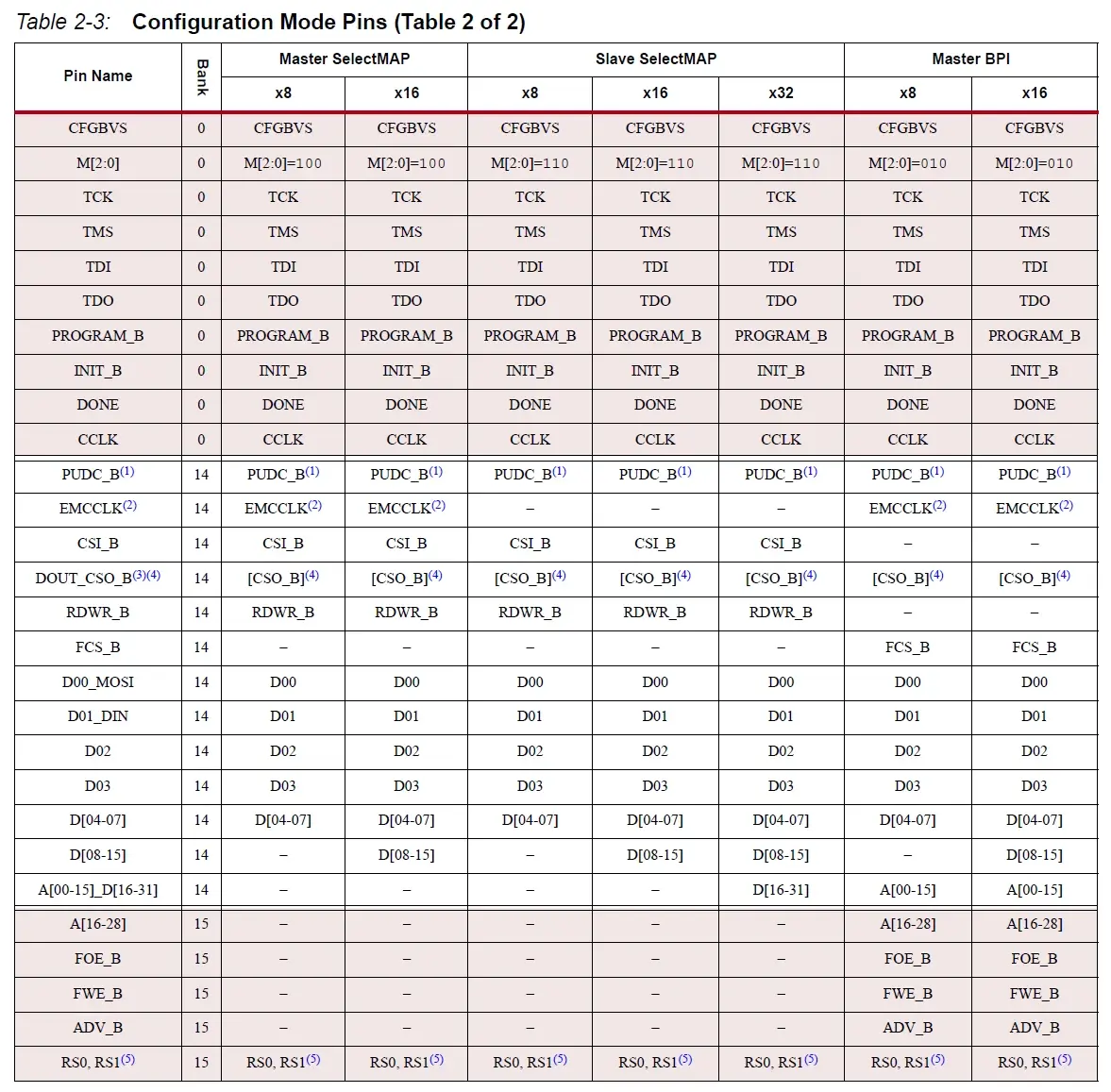

每组配置模式都有一组特定的接口管脚,它们跨越7系列FPGA上的一个或多个I/O BANK。7系列器件支持3.3V、2.5V、1.8V或1.5V的I/O配置,包括:

BANK 0 中的JTAG管脚、BANK0中的专用配置管脚

BANK14和BANK15中与特定配置模式相关的管脚

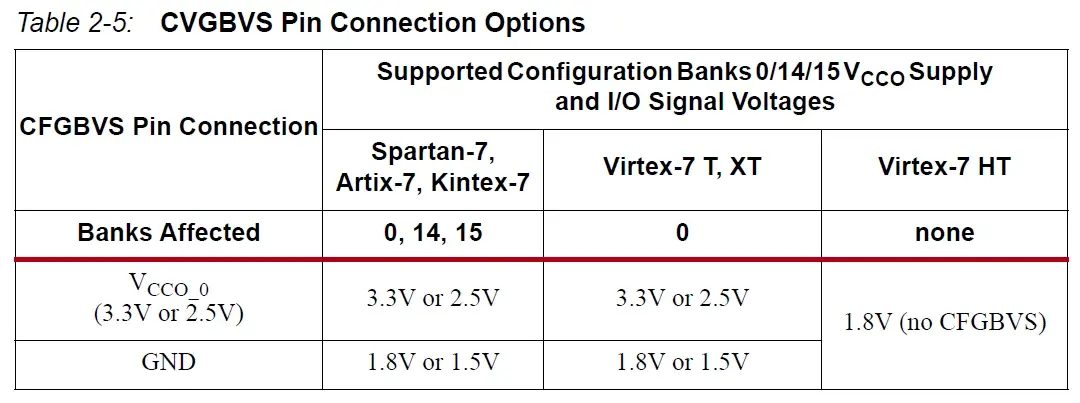

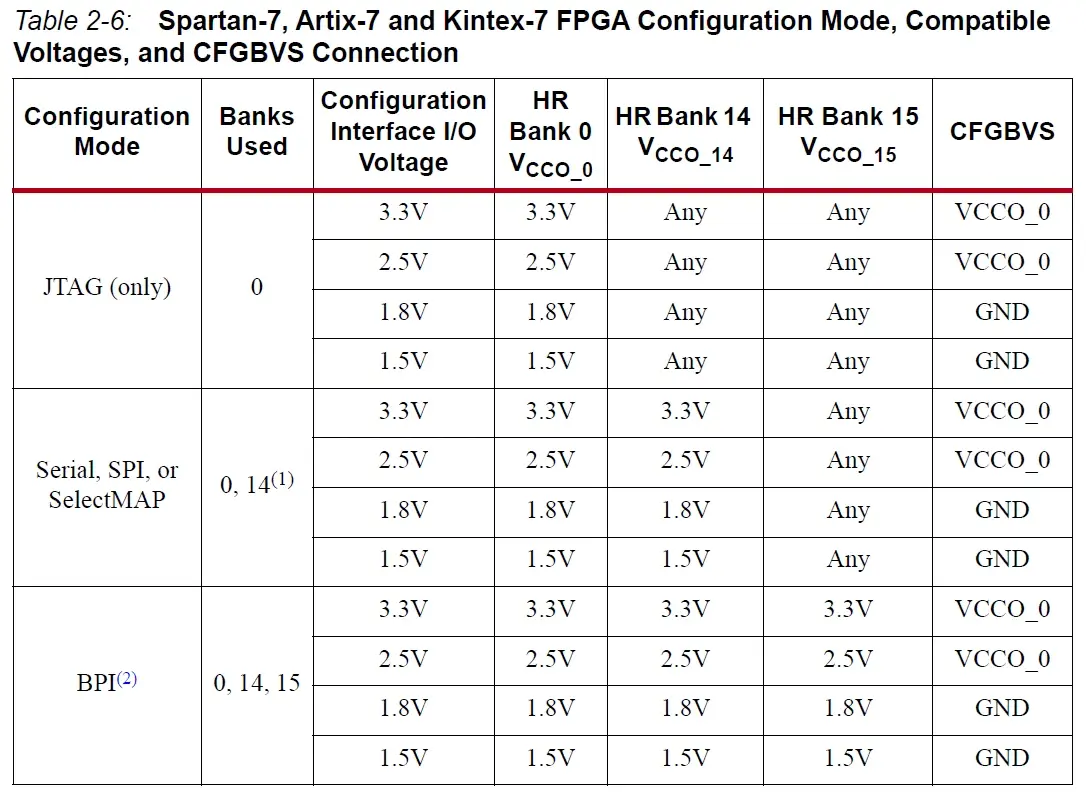

I/O电压配置由CFGBVS(配置组电压选择引脚)确定:

当CFGBVS为GND,并且配置模式使用到BANK14/15时,VCCO_0、VCCO_14和VCCO_15必须为1.8/1.5V以避免器件损坏。具体的配置关系如下:

在Virtex‑7 FPGA中,BANK14和BANK15是高性能BANK,仅限于1.8V或更低的I/O标准,Virtex‑7 HT器件仅支持BANK0的1.8V操作。

所有专用输入引脚都在VCCO_0为LVCMOS电压电平(LVCMOS18、LVCMOS25或LVCMOS33)下工作。所有有源专用输出引脚均在VCCO_0电压电平下工作,输出标准设置为LVCMOS、12mA驱动、快速摆率。

一般来说专用引脚除了电平外不需要额外进行配置

具体的配置模式所对应的管脚如下:

在进行电路板设计时,需要严格对照管脚映射,否则会导致配置失败。

注意事项:

1. PUDC_B在配置过程中具有特殊功能,它独立于所有配置接口,不需要与配置接口中其他引脚电压兼容。

2. 仅当 BitGen ExtMasterCclk_en 选项启用 EMCCLK 作为主配置模式时钟的输入时,才使用 EMCCLK。

3. DOUT 仅用于串行配置菊花链,用于将数据输出到下游 FPGA(或 用于 BitGen 调试比特流 选项)。否则,DOUT 是高阻状态。

4. CSO_B仅用于并联配置菊花链,用于将芯片使能信号输出到下游设备。否则,CSO_B为高阻状态。

5. RS0 和 RS1 仅在启动多重引导事件或启用 BitGen 配置回退选项并发生回退事件时驱动。否则,RS0 和 RS1是高阻状态。使用 RS[1:0]引脚进行配置时,建议不要在用户模式下使用它们。

6. 空单元格表示引脚在配置模式下未使用,在配置过程中被忽略且为高阻。

1.3.1 PROGRAM_B引脚

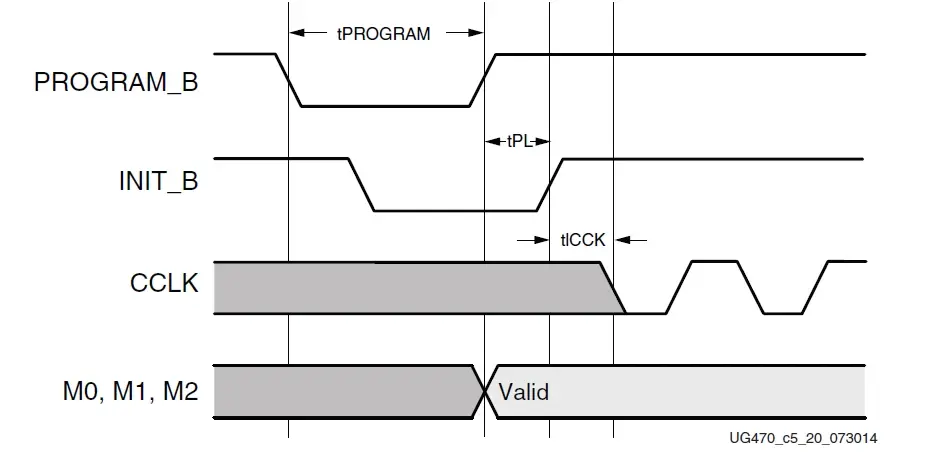

低电平有效。当PROGRAM_B脉冲为低电平时,FPGA配置被清除并启动新的配置序列。配置复位在下降沿启动,配置(即编程)序列在下一个上升沿开始。

在上电时将PROGRAM_B保持为低电平不会使FPGA配置保持在复位状态。相反,使用INIT_B来延迟上电配置序列。

1.3.2 INIT_B引脚

低电平有效。当FPGA处于配置复位状态、FPGA正在初始化(清除)其配置存储器或FPGA检测到配置错误时,FPGA将该引脚驱动为低电平。

完成FPGA初始化过程后,INIT_B被释放到高阻态,此时外部电阻器应将INIT_B拉高(将INIT_B连接到一个 的上拉电阻到VCCO_0)。当初始化过程完成后在INIT_B输入检测到高电平时,FPGA继续执行由M[2:0]引脚设置指示的配置序列的其余部分。

1.3.3 DONE引脚

高电平有效。DONE引脚上的高电平信号表示配置序列完成。DONE输出默认为开漏输出。

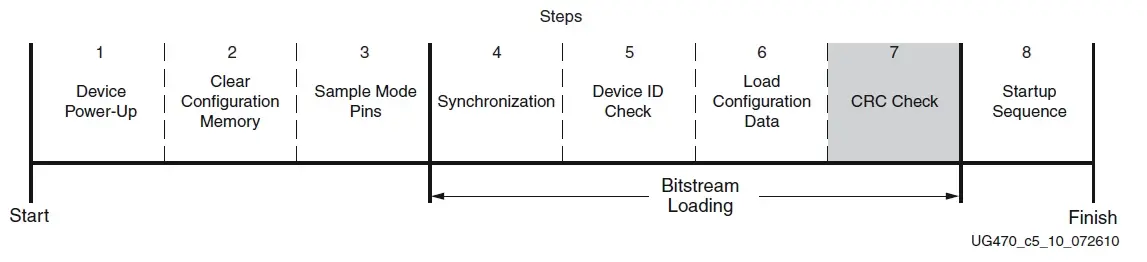

1.4 配置流程

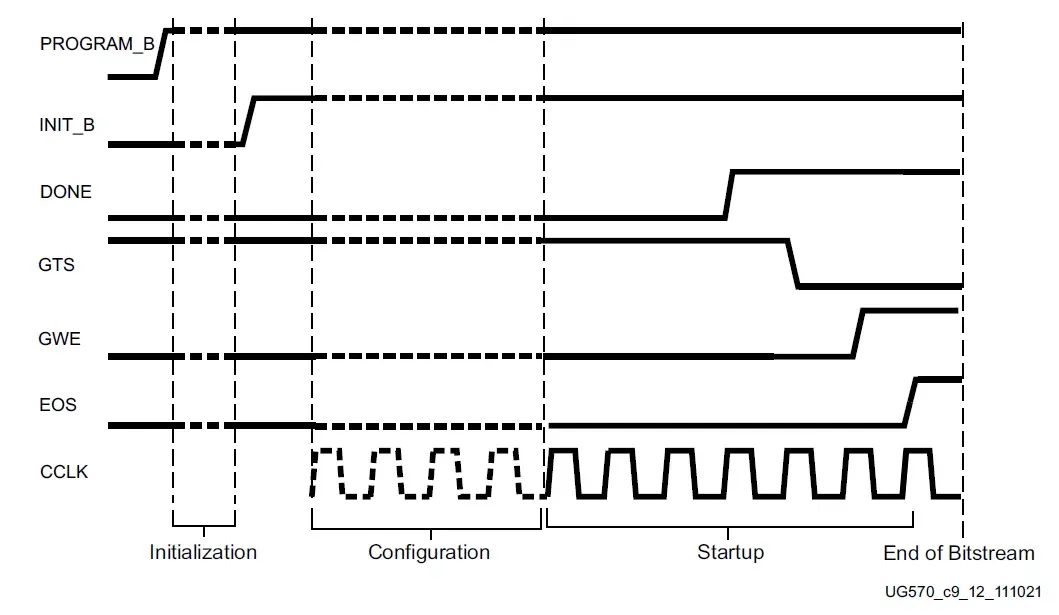

对于所有配置模式,7系列的基本配置流程都是相同的,主要可以分为三个大块:设备启动,数据流加载,启动序列。

1.4.1 设备上电

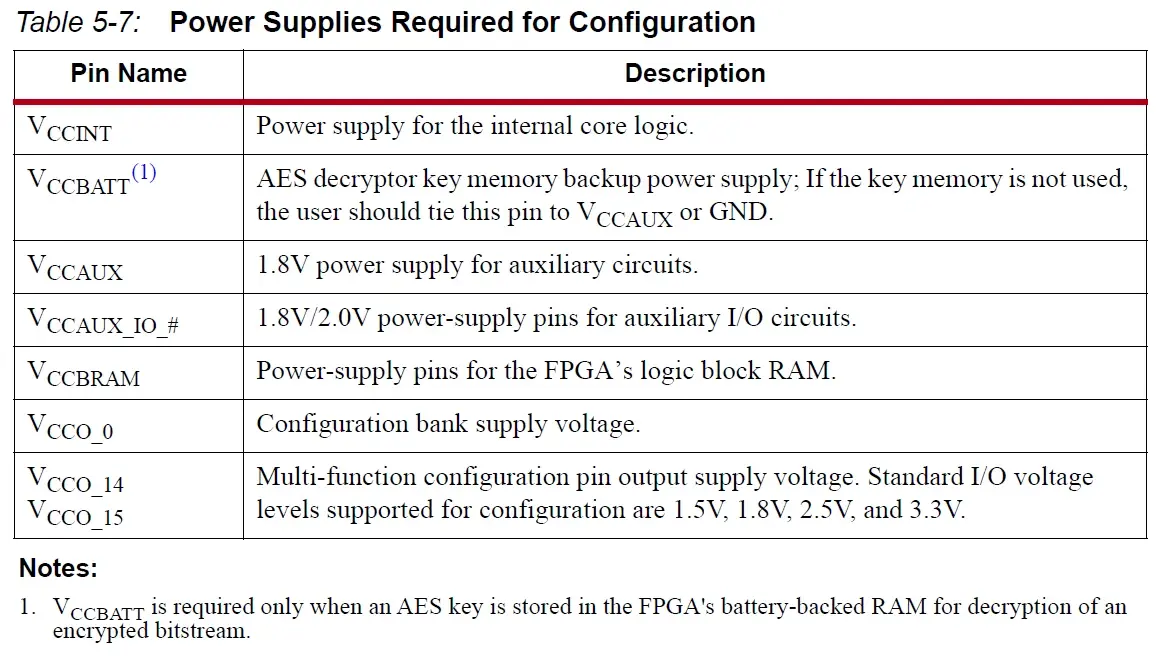

配置流程的第一步自然是设备上电,这里也就解释了为何固化程序后需要下电再上电才能生效。配置涉及到的电源如下:

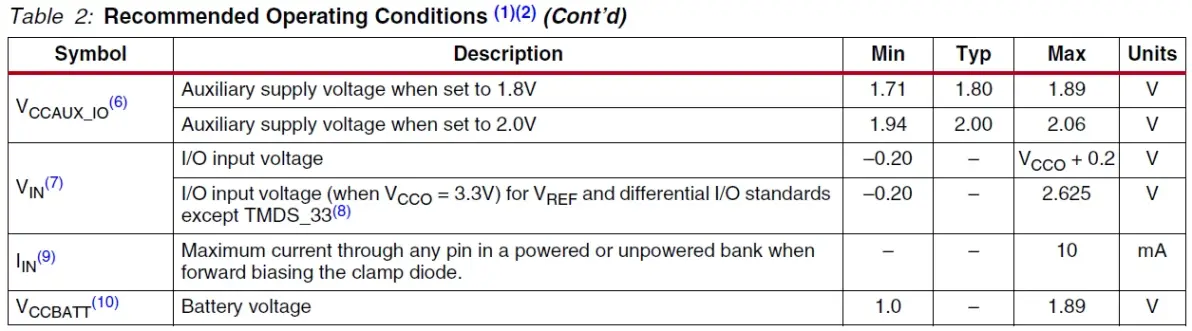

VCCO_0以及VCCO_14、VCCO_15在前文已经提及,其他的电源需要参照对应的数据手册推荐值进行配置,例如K7对应手册【DS182】:

FPGA在设备启动阶段的时序关系:

TPOR:Power-on Reset (POR);TICCK:CCLK Output Delay

FPGA上电启动后电压达到VCCO后在10~50ms后INIT_B信号拉高,初始化完成,FPGA开始加载配置工作。

上电后可以通过拉低将PROGRAM_B引脚切换为低电平来重新配置器件:

INIT_B在初始化期间被内部驱动为低电平,然后在上电情况下(第一次上电配置)在TPOR之后释放,在其他情况下(触发退回或者重配置等)在TPL之后释放。如果INIT_B引脚在外部保持低电平,则器件在初始化过程中的这一点等待,直到该引脚被释放,并且需要满足TPOR或TPL延迟。

FPGA上电第一次加载与PROGRAM_B没有关系,只要达到延迟时间,FPGA就会初始化完成,INIT_B信号拉高,直接进入配置数据过程。只有第二次重新配置才使用PROGRAM_B。

图中的时间参数可以在对应的FPGA数据手册中查看,如K7系列对应【DS182】:

1.4.2 清除配置寄存器

在器件上电后、PROGRAM_B引脚脉冲低电平后、使用JTAG JPROGRAM指令或IPROG命令后或在回退重试配置序列期间,配置存储器会顺序清除。在此期间:

Block RAM被重置为其初始状态,并且触发器通过全局设置重置(GSR)的断言重新初始化。除少数配置输出引脚外,I/O通过使用全局三态(GTS)置于High Z状态,如果PUDC_B为低电平,则内部上拉。

PUDC_B用于设置配置期间的上拉,低电平有效,电路上通过直连或者≤1kΩ连接到VCCO_14或GND,禁止悬空。

清除配置寄存器发生在INIT_B为低的这个阶段。通常这个时间为3ms。

3ms的时间来自于复旦微的手册中:JFM7K325T清除配置寄存器时间为20ms,而对标产品为3ms。在从模式中推荐等待INIT_B拉高再进行配置。

1.4.3 采样模式引脚

当INIT_B引脚转换为高电平时,器件对模式引脚M[2:0]进行采样并开始驱动CCLK(如果处于主模式)。此时,器件开始在配置时钟的上升沿对配置数据输入引脚进行采样。

对于BPI和SelectMAP模式,总线宽度最初为×8,可以在状态寄存器查看。在总线宽度检测序列之后,状态寄存器被更新。从串行、主串行、SPI和JTAG模式忽略总线宽度检测模式。

只有在通过电源循环或PROGRAM_B置位进行重新配置时,才会再次对模式引脚进行采样。

1.4.4 同步

FPGA正常数据加载前,需要做一个FPGA与配置方(如FLASH)之间的同步检查。方法是将一个特殊的32位同步字(0XAA995566)发送到FPGA。同步字会提醒FPGA即将到来的配置数据并将配置数据与内部配置逻辑对齐。

除“总线宽度自动检测”序列外,同步之前配置输入引脚上的任何数据都将被忽略。

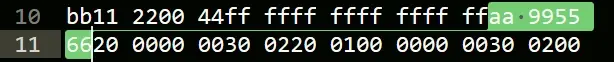

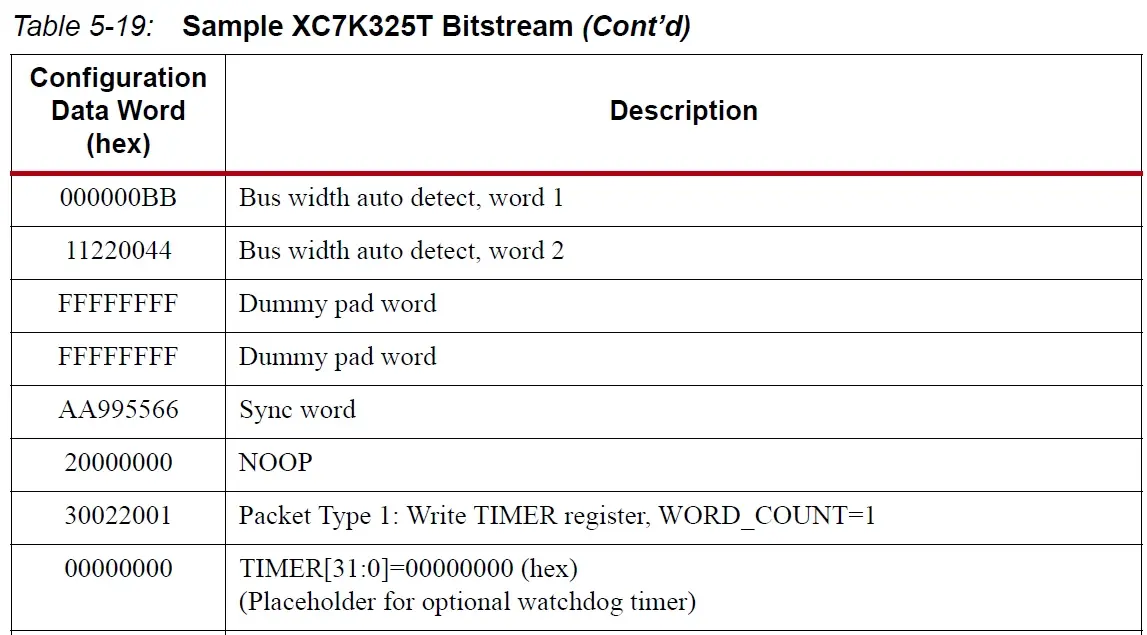

Xilinx在生成的.bit文件中已经自动加入了这个同步字。可以进行查看:

表5-19说明了bit流的定义:

1.4.5 检测设备ID

设备同步后,必须通过设备ID检查才能加载配置数据帧。这可以防止配置具有针对不同设备格式化的比特流。如果在配置期间发生ID错误,设备会尝试执行回退重新配置。

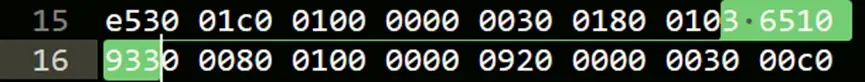

设备ID检查内置于比特流中,器件ID检查是通过配置逻辑的比特流中的命令执行的,而不是通过 JTAG IDCODE 寄存器。ID可以在【UG470】的表1-1中查找到,例如7K325T对应3651093,可以在bit文件中查找到:

1.4.6 加载配置数据

在准备工作完成后,FPGA开始加载配置数据。在这个过程中,FPGA的所有可配置I/O根据HSWAPEN引脚的设置变为弱上拉(HSWAPE=1)或者高阻态(HSWAPE=0)。这个阶段的I/O引脚还没有变为用户需要的状态,也最有可能影响到其他外围电路的上电时序和运行。

设计硬件电路时要特别注意并采取必要措施,如加入上下拉电阻或改变器件加电顺序来尽量避免或减少FPGA配置时对电路其他器件的影响。

1.4.7 CRC校验

加载配置数据帧时,器件会根据配置数据包计算循环冗余校验(CRC)值。加载配置数据帧后,配置比特流可以向设备发出校验 CRC指令,然后是预期的CRC值。如果设备计算的 CRC 值与比特流中的预期CRC值不匹配,则设备将INIT_B拉低并中止配置,此时用户必须把PROG-B引脚拉低,才能进行重新配置。

默认情况下,CRC校验包含在配置比特流中,如果禁用CRC检查,则存在加载错误配置数据帧的风险,从而导致错误的设计行为或损坏器件。

1.4.8 启动序列

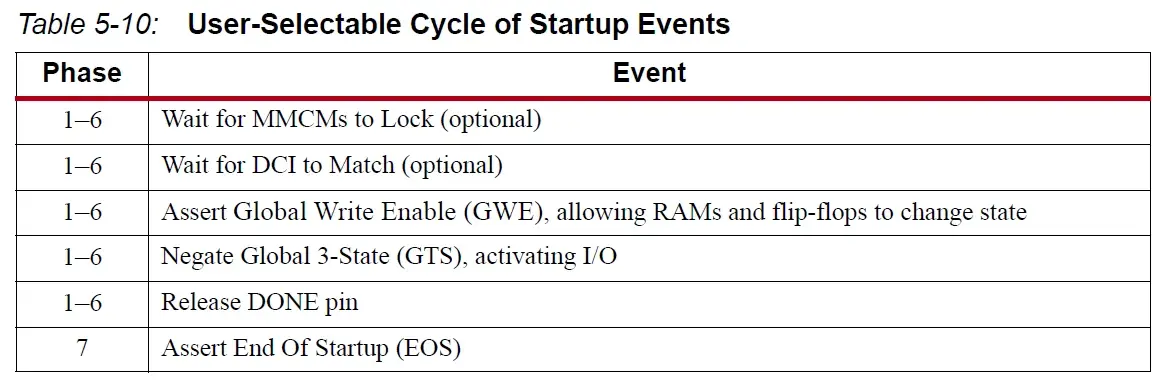

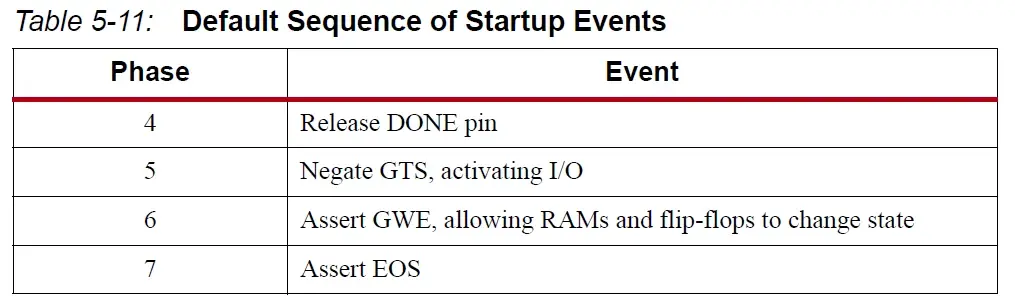

加载配置帧后,FPGA不会马上执行用户的逻辑,比特流指示设备进入启动序列。启动顺序由8阶段(阶段0-7)顺序状态机控制。用户可以选择每个启动事件的特定阶段(见【UG628】):

可以强制启动序列等待 MMCM 锁定或等待DCI与适当的选项匹配。这些选项通常设置为在MMCM锁定和/或DCI匹配之前防止DONE、GTS和GWE被断言(防止设备操作)。

默认情况下,启动顺序:

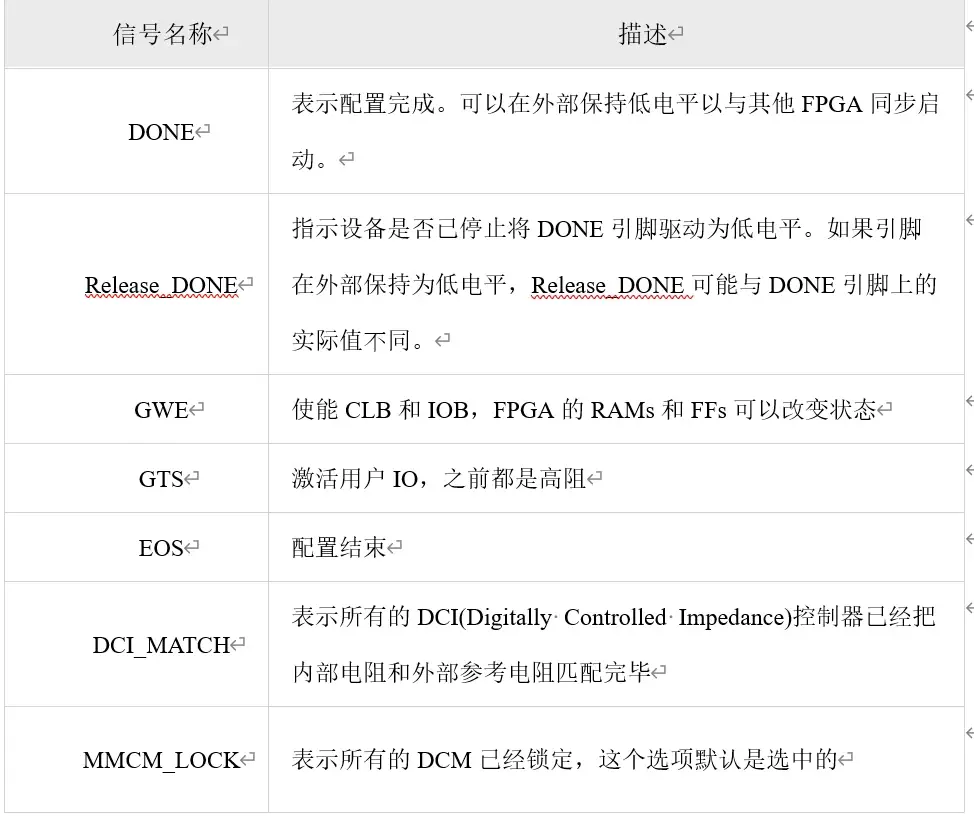

与启动相关的信号:

DONE信号可通过DONE引脚或7系列FPGA状态寄存器获取,其余只能通过7系列FPGA状态寄存器获取。对应的信号时序如下:

从上图可以看出:

FPGA最后的Startup过程有8个周期,其中DONE变高仅仅是第4个周期。因此,在DONE变高之后还需要再给3个CCLK。否则DONE虽然变高了,FPGA程序并没有正确运行。

ISE会在设计中搜索用户是否使用了DCI,如果是,FPGA会使用2个周期的Start UpPhase,等待DCI匹配上。即FPGA会在那儿等待,直到DCI匹配上。如果我们在上位机读取了配置文件,获得了文件大小,我们把它写到负责加载FPGA的Flash里,然后CCLK时钟就不给了。这就产生问题,因为DCI匹配需要时间,我们的问题就是,过了一段时间,DCI匹配完毕了,但是CCLK却没有了,因此FPGA一直处在Start UP的前2个Phase上,不会到DONE。导致无法配置成功。

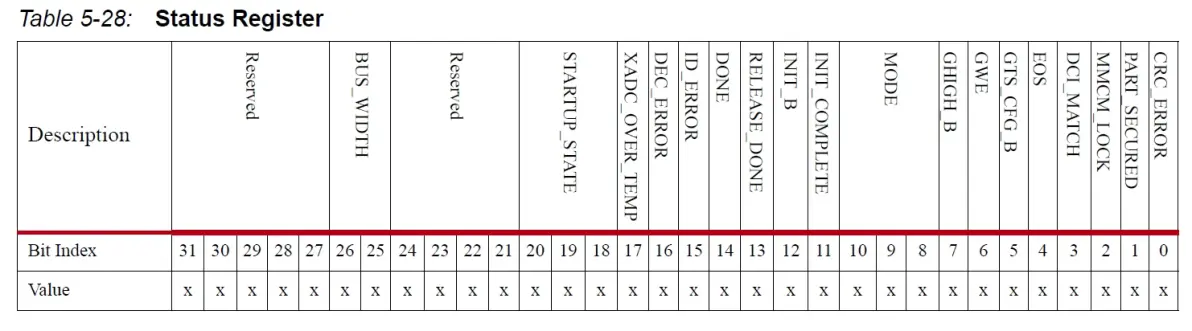

1.4.9 配置状态字寄存器Status Register

Xilinx的FPGA有多种配置接口,如SPI,BPI,SeletMAP,Serial,JTAG等;如果从时钟发送者的角度分,还可以分为主动Master(即由FPGA自己发送配置时钟信号CCLK)和被动Slave(即由外部器件提供配置所需要的时钟信号);另外还可由板上稳定晶振提供时钟信号,经由FPGA的EMCCLK接口,再从CCLK端口送出。

如此多的配置形式,一旦发生配置失败怎么办?大家都知道先要查看一下板子上FPGA的DONE管脚。但绝大多数情况下,DONE管脚此时会是低电平,只能证明配置确实失败了。但是失败的原因到底是什么呢?调试到底应该如何入手呢?

FPGA的状态字寄存器Status Register能直接告诉你或者极大地辅助判断失败的原因,Xilinx FPGA的状态字,在赛灵思所有器件系列中都基本保持一致的定义(个别位由于系列特性不同可能有细微区别,这些不是最重要的,不在我们今天讨论的范围内)。

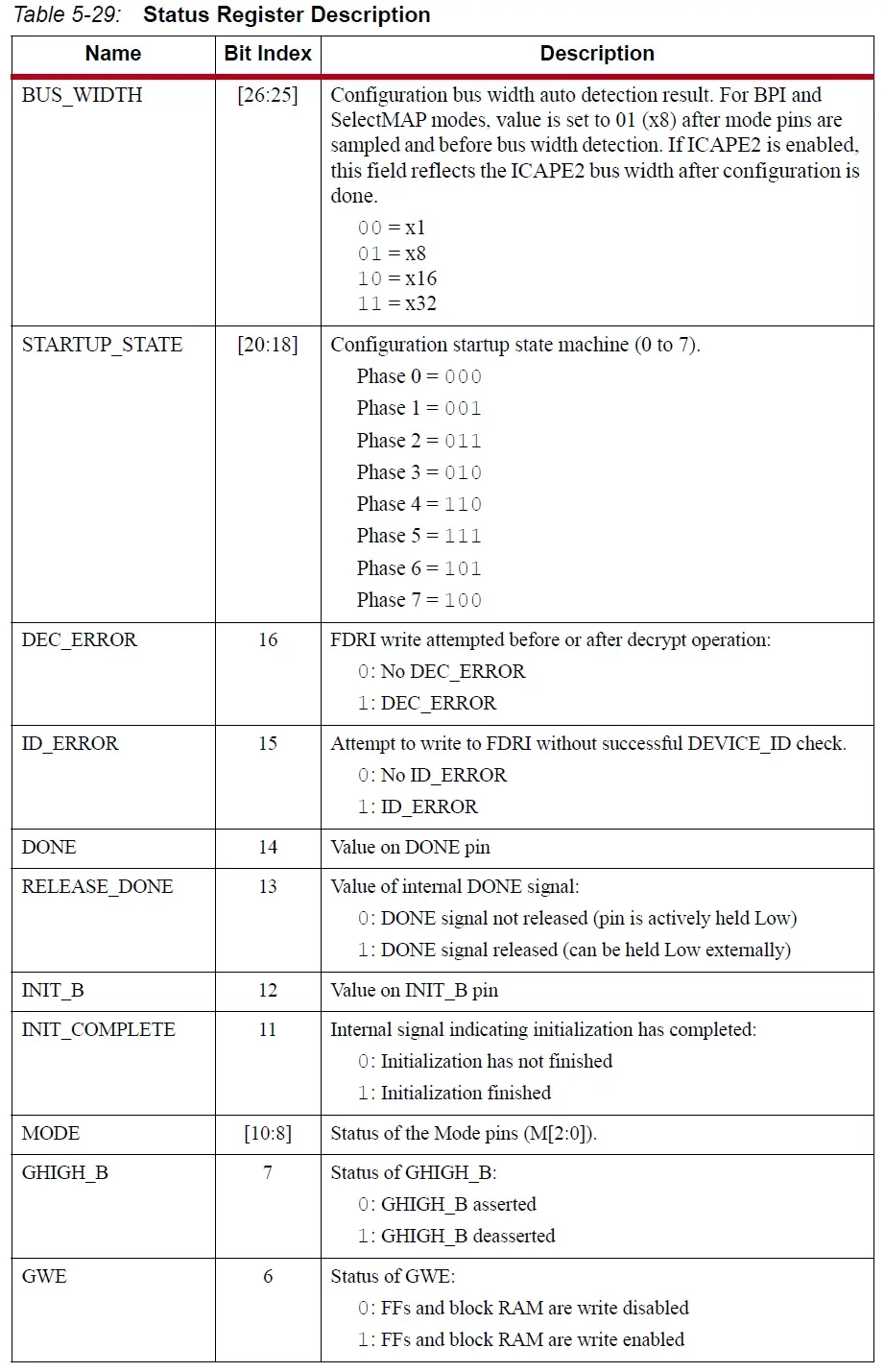

以7系列 FPGA为例,我们看看UG470上对状态字的完整定义:

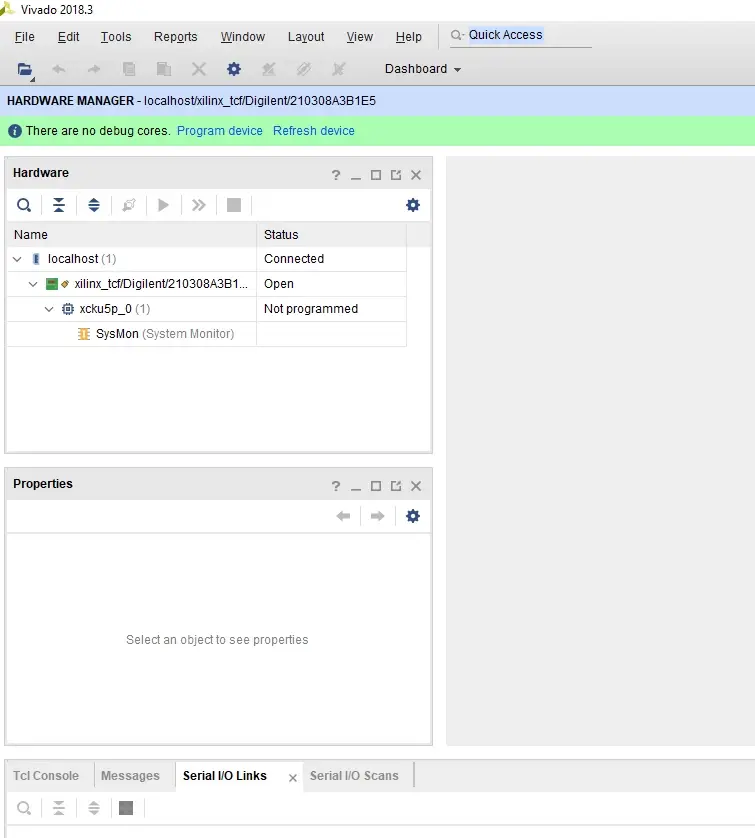

首先,用下载线连接好板子和电脑,板子上好电。打开Vivado硬件管理器,扫描板子上的JTAG链 (Open target -AutoConnect), 板子上的JTAG链中的器件会显示在Hardware窗口中:

鼠标选中扫描出的FPGA器件,在下方的Hardware Device Properties窗口中,选择Properties项,会出现该FPGA的一系列属性。找到其中的REGISTER分类,展开,第二个寄存器CONFIG_STATUS, 即是我们要讨论的状态字了。

这里可以看到的是一个配置前的状态字的标准状态:

只有BIT02 PLL_LOCK, BIT03 DCI_MATCH, BIT11 INIT_B_INTERNAL, BIT12 INIT_B_PIN的值必须是1;

BIT08-10 MODE PINS,BIT21 SECURITY_STATUS, BIT25-26 BUS_WIDTH,BIT28 PUDC_B根据FPGA和板子具体的设定,可以为1或者0,其他都必须是0。

如果一上电,状态字就表现出了非典型值,那么大概率硬件上就有错误或者不合理的地方了。比较典型的几个例子:

1. 状态字全0

REGISTER.CONFIG_STATUS 00000000000000000000000000000000

这种情况,说明FPGA被强行控制在全局复位状态了。一般是硬件上PROGRAM_B管脚,或者INIT_B管脚被错误的拉到了地上,两个管脚上的有效电平为0.

非常偶尔的情况下,当DONE管脚被错误拉为0电平时也能出现此种状态字。

2. 状态字全1,或者一串1后面跟着一个到数个0(一般不超过4个)

REGISTER.CONFIG_STATUS 11111111111111111111111111111111

REGISTER.CONFIG_STATUS 11111111111111111111111111111110

REGISTER.CONFIG_STATUS 11111111111111111111111111111100

这种一般是板子上设计的JTAG链里面不只一个FPGA器件,比如是Xilinx的FPGA和一个第三方的CPLD串联等。

由于Vivado里面并没有第三方器件的BSDL文件,那么在扫描整个JTAG链时,它无法识别链中各器件的型号以及数目,所以往往从TDO管脚中移位出一串1来。如果Xilinx的FPGA位于链的末端(接近TDO的位置),那么有时可以识别出正确的FPGA型号。但是这种情况仍然无法正确进行将要进行的配置操作。另外很多例子中则是FPGA的型号也被识别错误了。

解决方案如下:

https://www.xilinx.com/support/answers/61312.html

3. Unknown Device/Many Unknow Devices

此时,不要说状态字无法检测了,整个JTAG已经无法正确扫描,Vivado里面无法识别出任何器件。这一般是板子上的JTAG接口的TDO或者链中最后一个器件的输出管脚TDO,被短接到了地平面上。

除了上述典型情况,当然还有很多一上电就无法继续配置的情况,原因不胜枚举。这种情况下请详细描述你的JTAG链构成,读出当前的状体字(如何还能够读的话),如果状态字正常,可以接下来进行配置操作。或者是在你的配置失败后,保留失败现场再连接好板子和电脑继续读出状态字。

如果你的板子已经重新上下电了,那么当时失败的场景也就消失了。这也就是我们一再强调失败后要保留现场,板子上要保留JTAG接口的原因。当然在设计成熟后,或者实验室调试工作结束后,可以去掉JTAG接口以期得到产品更高的安全性。

配置完成后,得到的状态字如下:

REGISTER.CONFIG_STATUS 00010010100100000111110111111100

注意其中的:

BIT02 PLL_LOCK, BIT03 DCI_MATCH, 绝大多数情况已经变为1;

BIT04 EOS,BIT05 GTS, BIT06 GWE, BIT07 GHITH,以及BIT11 INIT_BINTERNAL, BIT12 INIT_B_PIN,BIT13 DONE_INTERNAL, BIT14 DONE_PIN必然是1;

BIT18-20 STARTUP_STATTE应该是100;

BIT25-26 BUS_WIDTH应该是检测出了正确的配置位宽,或者在serial的情况下,保持默认的01值;

其他BIT01 DECRYPTOR, BIT09-10 MODE_PINS, BIT21-23 SECURITY_STATUS, BIT28 PUDC_B, BIT30CFGBVS_PIN, 根据你的使用,有可能是其他的0或者1组合。

RESERVED的不用管。

如果不是这种结果,那么就要看看出什么问题了。

在一些相对简单,典型的情况下,只看某一位就可以直接得到想要的答案。

BIT00的CRC error为1

在不是状态字全1的情况下CRC error位为1,说明配置出现了CRC错误。这是一种很常见,但比较难修复的错误,因为CRC错误的原因一般是因为板子上的信号质量(SI, Signal Integrity)不行,传输数据的过程中0/1电平判决错误,导致配置数据写入失败。

如何确定真的是SI问题呢?看失败概率。CRC错误一般是随机出错的,并不一定100%失败(除非板子的信号差得没法用了,这个一般不会)。那么配置文件中01翻转的次数越少,出错的概率越小。你可以生成一个只点亮板上一盏LED的小测试设计,此时bit文件中有效数据(1)非常少,试着下载该bit看看,是不是配置失败率降低了?如果是,那么基本可以确定了。

一旦出现这种情况,可以尝试的办法有:

1. 降低CCLK频率

2. 在CCLK的输入端(以及输出端),加入合适的端接电路

3. 换用更高质量的配置时钟(比如使用质量较好的晶振通过EMCCLK提供时钟)

4. 改善数据链路的信号质量,如果对待CCLK,同样在数据通路上加入合适的端接匹配电路。

总而言之,要做的就是改善板上的信号质量。如果板子SI实在太差,那只有改板,或者尝试下其他配置方式了。

其他位都正常,BIT13 DONE_INTERNAL也为1了,但是BIT14 DONE_PIN为0,FPGA不工作!

这种情况,其实配置数据已经完整、正确的送入FPGA并且被接收了,但是FPGA的DONE管脚连接不正确,导致DONE没有或者没有在规定时间内上拉到要求的电平,从而导致FPGA最终的启动失败。

Xilinx的FPGA,一般要求DONE管脚上外加一个上拉电阻(330欧, 4.7K欧等,不同系列要求不同,请参照对应的Configuration User Guide)。如果这个上拉电阻没有加,或者加的阻值过大或过小,那么DONE管脚无法在规定的时间里面达到高电平,此时内部配置控制器会认为配置失败了,典型情况就是DONE internal为高(内部数据接收完毕,内部释放了),但是DONE外部管脚为低。

此时需要做的,就是检查PCB上DONE部分的设计,看看是不是有和其他管脚相连的情况,被其他管脚强行拉低了。或者是设计的DONE点亮LED灯电路不合理, LED通电后把DONE管脚的电平降为低电平。

如果你不清楚如何设计这部分电路,从 www.xilinx.com 上,找到一款和你使用的FPGA型号相同或者同系列的开发板,参考它的原理图设计。

BIT29 BAD PACKET error

Bit29为1,大概率也是CRC错误。这不过这个CRC错误比较特殊,出错位跑到了配置文件里面的命令上,导致配置命令变成了一个无效无意义的指令。此时状态字会报出bad packet error。

和CRC错误的随机性一样,多次重复加载过程,大概率出错的数据位下次落到其他的数据上。由于配置数据的数量远远大于配置命令,那么很有可能下次出错看到的是BIT00 CRC ERROR为1.

如果每次都是BAD PACKET error,更要怀疑使用的配置文件已经损坏。比如进行了非法改写。Xilinx的任何配置文件,都是禁止手工修改的。

BIT15 IDCODE Error为1

配置文件下载时,都要先经过FPGA的IDCODE校验。如果这一步通不过,那么后续的配置不会进行。这种情况下,看看配置文件的bit/bin/mcs是不是给错了。或者FPGA器件有silicon revision的变化。举个例子,有的系列ES芯片和Production芯片的配置文件是不能兼容的。这种错误情况,如果是用JTAG通过Vivado下载,那么log里面也会有相应的提示。

BIT13 DONE_INTERNAL+ BIT14 DONE_PIN均为0

这也是一种较常见的错误。此时要重点检查一下BIT07 GHIGH位,看看它是不是1。如果是,那么大概率是,你的CCLK时钟给的不够多。FPGA在接收完所有的配置数据后,还需要一定数量的CCLK时钟去完成内部的初始化。如果发送端,此时常常是一个CPU用Slave模式加载,认为有效数据结束,强行停止了进一步的时钟发送,那么有时可以观测到此种状况。此时去检查BIT18-20 STARTUP_STATE,根据具体的情况,也有一定概率看到不是预期的100.

标准的做法是,在默认设置下持续发送CCLK时钟,直至检测到DONE管脚已经拉高,然后再多发送至少64个时钟信号。如果修改了配置默认设置,比如选择了wait for PLL to lock,那么需要更多的时钟信号。

状态字看起来和没有发出配置数据,即和刚上电的表现一样。

这种情况,说明所有发出的配置数据都被FPGA忽略掉了,因为它不认为你发送过来的是有效配置数据。

FPGA的配置文件里面,有一个数据同步头,一般是AA 99 55 66。如果由于某种原因,这个同步头FPGA都没有认出来,那么后续的数据会被它全部忽略。

一般的原因是:

1. 在非serial配置模式中,没有正确的做Byte Swap;

2. 配置文件生成时,BPI数据线宽设置不对(x8, x16, x32选错了)

3. SPI的x1, x2, x4选择错误;

4. 严重的板级SI问题导致的CRC错误;

以上列举了常见的一些配置错误和其状态字的相应表现。需要注意的是,状态字寄存器有32位,其组合可以说是相当多的。除了上述情况,配置失败定位还可能需要结合状态字,加载过程中log文件,硬件设计原理图和工具版本信息,以及通过其他一些配置接口在不同条件下去对比测试才能逐步定位。

2.4.10 注意事项

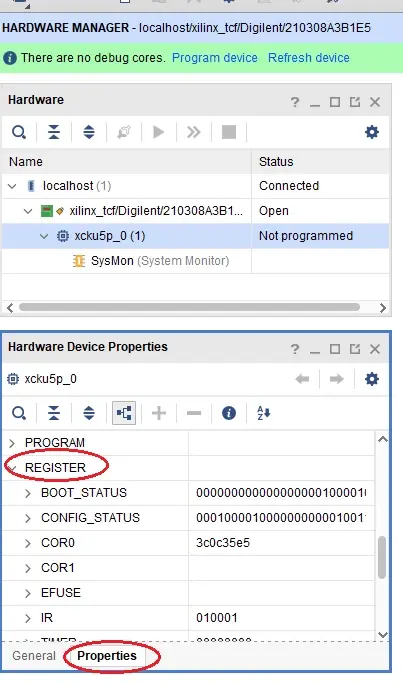

启动结束时的I/O转换

在Spartan-7、Artix-7和Kintex-7系列中,在HR I/O BANK上具有多功能配置管脚,如果 BANK 的VCCO为1.8V或更低,并且如果该BANK上的管脚为低或浮动,则输入可能在配置启动期间有一个 0-1-0 转换到互连逻辑。

由于此转换发生在 GWE 启用内部逻辑之后,因此可能会影响配置后设备的内部状态。转换发生在EOS(启动结束)之后的一个CFGCLK。

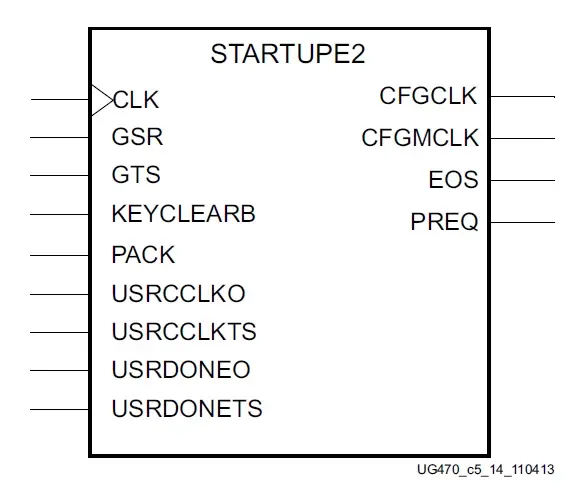

为避免这种转换,可以将VCCO_14和VCCO_15设置为2.5V或3.3V,或从外部将引脚驱动为高电平(参见表5-13)。否则,逻辑应设计为忽略这些受影响的输入信号,直到EOS上升沿之后的一个 CFGCLK后至少200ns。可以使用 STARTUPE2原语监视CFGCLK和EOS。

STARTUPE2可以在设计中实例化,以在设备操作期间为用户提供对所选配置信号的控制。

DCI与多功能配置引脚配合使用

如果在用户设计中为I/O BANK14或15中的任何配置管脚分配了DCI I/O标准,则 DCIRESET原语也应包含在设计中并使用。

设计应该脉冲DCIRESET的RST输入,然后等待LOCKED信号被断言,再使用具有DCI标准的多功能配置引脚上的任何用户输入或输出。当多功能配置I/O引脚作为配置引脚执行时,它们会忽略器件初始化期间发生的初始 DCI 校准。

预防加载失败

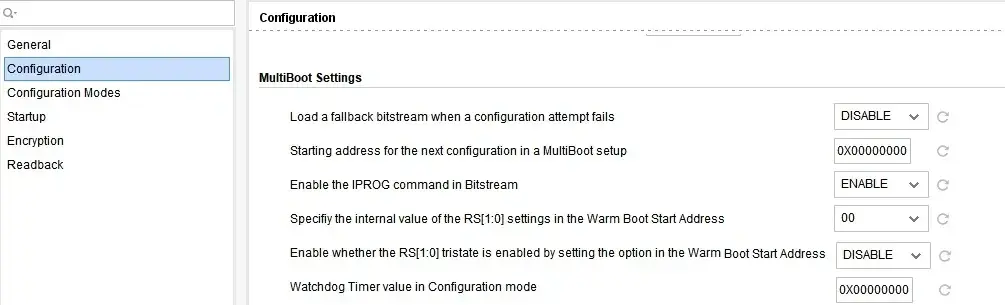

在设计时,为了减小外部电源抖动造成从外部存储程序器读取配置数据丢失和误码问题,可以使用multiboot中的看门狗功能,设置一个较大的计数值,当加载失败后触发回退功能,进行重新加载。配置方式Tools-> settings,在bitstream的additional settings中:

当回退发生时,内部生成的脉冲会重置整个配置逻辑,但专用MultiBoot逻辑、热启动起始地址(WBSTAR)和启动状态(BOOTSTS)寄存器除外。此复位脉冲将INIT_B和DONE拉低,清除配置存储器,并从地址0重新启动配置过程,其中修订选择(RS)引脚驱动为 00。复位后,比特流覆盖WBSTAR起始地址。

触发回退的情况:

IDCODE 错误

CRC 错误

看门狗定时器超时错误

BPI 地址环绕错误

嵌入式 IPROG 在回退重新配置期间被忽略。看门狗定时器在回退重配置期间被禁用。如果回退重新配置失败,配置停止并且 INIT_B 和 DONE 都保持低电平。MultiBoot和回退功能可用于所有主配置模式。