时间:2025-03-20 来源:FPGA_UCY 关于我们 0

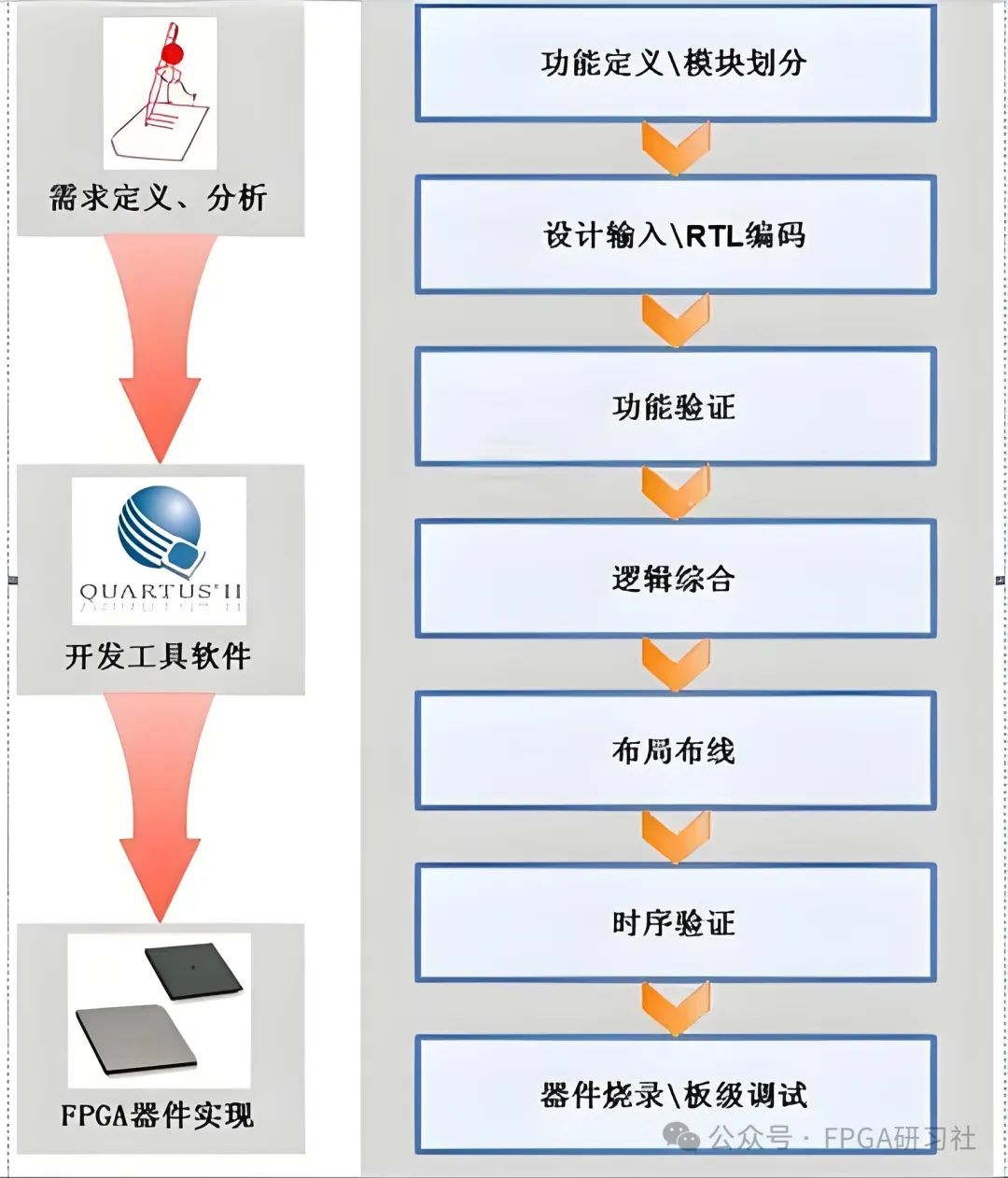

初涉FPGA领域的小白,常常在面对FPGA开发时感到迷茫,搞不清楚开发究竟有哪些流程,也不了解这些流程背后的目的和底层原理。别担心,今天这篇文章将带你深入探索,全面解析FPGA开发的七大流程,为你揭开FPGA开发的神秘面纱 。

1. 设计输入

目的

将系统需求转化为硬件描述语言(HDL)或高级综合(HLS)代码,建立数字系统的逻辑模型。

原理

- 抽象层级:通过模块化设计(如分层架构)分解复杂功能,每个模块对应FPGA的逻辑单元阵列中的特定区域。

- 硬件映射:HDL代码中的`wire`、`reg`等元素直接映射到FPGA的物理逻辑门(如LUT、DFF)和互连资源。

关键操作

- 编写HDL代码(/VHDL)或C/C++(通过HLS)。

- 定义模块接口(输入/输出信号、时钟、复位等)。

2. 功能仿真

目的

验证设计的逻辑正确性,确保功能行为与需求规格一致。

原理

- 仿真模型:基于HDL描述的理想化时序模型,忽略物理延迟和功耗。

- 测试平台:通过激励信号()模拟真实输入,检查输出是否符合预期。

关键操作

- 编写测试平台(TB),注入测试向量(如时钟序列、数据输入)。

- 使用仿真工具(如、)运行时序波形分析。

3. 逻辑综合

目的

将HDL代码转换为标准门级网表(),适配目标FPGA的硬件资源。

原理

- 逻辑优化:

- 逻辑最小化:使用算法(如Quine-)合并冗余逻辑门。

- 时序优化:插入流水线寄存器平衡关键路径延迟。

- 资源映射:

- 将逻辑门映射到目标器件的LUT、触发器(Flip-Flop)等资源。

- 根据工艺库( )选择最优实现方式。

关键输出

- 标准单元网表(.edf/.sdc):描述逻辑门级连接关系。

- 资源报告:统计LUT利用率、触发器数量等。

4. 时序分析

目的

确保设计在目标FPGA上满足时序要求(如建立时间、保持时间)。

原理

- 时序路径模型:

- 逻辑延迟:组合逻辑门延迟、触发器传播延迟。

- 布线延迟:信号在金属线上的传播延迟(受物理距离、负载影响)。

- 时钟树分析:

- 建立全局时钟树(Clock Tree),平衡时钟偏移(Skew)。

关键操作

- 添加时序约束(SDC/SDF文件)。

- 静态时序分析(STA):检测关键路径是否超过允许延迟。

5. 布局布线(Place & Route)

目的

将逻辑网表映射到FPGA的物理结构,完成信号路由和资源分配。

原理

- 布局(Place):

- 模块划分:将功能模块分配到特定区域(如IO Bank、PLL区域)。

- 热点管理:高功耗模块分散布局以降低局部温度。

- 布线(Route):

- 分层布线:采用金属层堆叠结构减少延迟(如Artix-7的5层金属)。

- 物理效应管理:

- 串扰:通过差分走线或增加间距抑制。

- 电源噪声:优化电源地网络(PG Mesh)。

关键输出

- 布局后时序报告:包含实际延迟和时序违例情况。

- 物理实现图:显示模块位置、布线路径等。

6. 生成配置文件

目的

将布局布线结果转换为可编程的比特流(),用于配置FPGA硬件。

原理

- 配置架构:

- SRAM:上电加载,支持动态重配置。

- FLASH:非易失存储,无需每次上电加载。

- 编程过程:

- 通过JTAG、SPI等接口将比特流写入FPGA配置存储器。

关键操作

- 比特流生成:

- 根据目标器件生成对应格式的配置文件(.bit/.bin)。

- 验证配置:

- 使用边界扫描( Scan)检测引脚连通性。

7. 硬件验证

目的

在真实硬件平台上验证设计功能与性能。

原理

- 在线测试:

- 逻辑分析仪(ILA):实时捕获信号并对比预期值。

- 示波器:测量关键节点电压/时序(如时钟稳定性)。

- 功能验证:

- 验证设计是否满足原始需求规格(如吞吐量、延迟)。

关键操作

- 硬件平台搭建:连接电源、外设(如传感器、显示屏)。

- 回归测试:多次迭代验证设计鲁棒性。

关注本公众号,学习FPGA不迷路↓↓↓