时间:2024-08-09 来源:网络搜集 关于我们 0

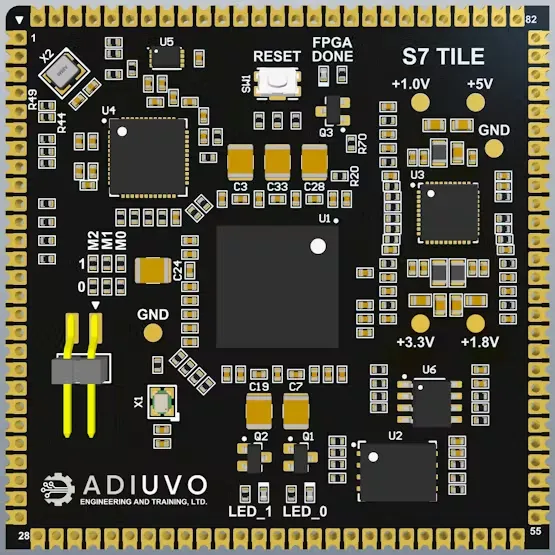

在AMD系列中,小型FPGA如AMD Spartan™ 7和AMD Artix™ 7非常适合多种应用,因为它们提供了可确定性、低延迟和非常灵活的 I/O。在这个项目中,将创建一个包含AMD Spartan 7 FPGA及其支持组件的小型模块,以制作一个"芯片"。这个"芯片"将是一个简单、小巧的印刷电路板,可以轻松地被包含在其他项目中,从而避免了每次都需要从头开始设计的麻烦。 我们的目标不仅仅是要制作一个尽可能小巧且低成本的模块,同时也要为之前另一个项目中剩余的几个Spartan 7 FPGA设备找到用途。该项目将解决需求开发、架构、组件选择和原理图设计的问题。一旦完成,我将把电路板送出去进行布局和制造。将有一个后续项目,包括测试和启动 Spartan 7 FPGA stamp。原理图和布局将以源格式提供给需要它们的人。

我们的目标不仅仅是要制作一个尽可能小巧且低成本的模块,同时也要为之前另一个项目中剩余的几个Spartan 7 FPGA设备找到用途。该项目将解决需求开发、架构、组件选择和原理图设计的问题。一旦完成,我将把电路板送出去进行布局和制造。将有一个后续项目,包括测试和启动 Spartan 7 FPGA stamp。原理图和布局将以源格式提供给需要它们的人。

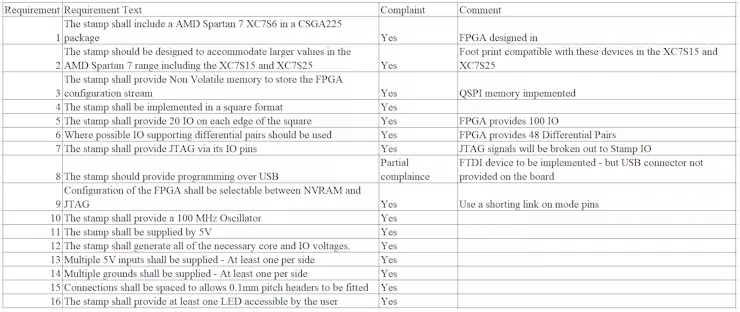

所有项目都应当以一套需求开始,这些需求定义了项目的功能和非功能性行为。这些需求还将提供接口需求。

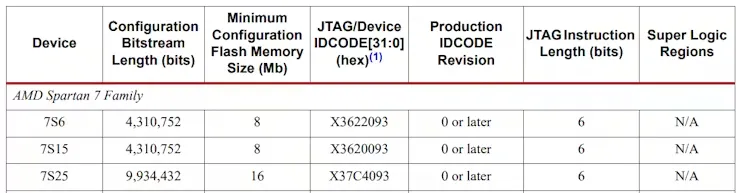

REQ1 - 该模块必须包含一个AMD Spartan 7 XC7S6 FPGA,采用CSGA225封装。

REQ2 - 该模块应该设计得能够适应AMD Spartan 7 FPGA系列中的更大型号,包括XC7S15和XC7S25。

REQ3 - 该模块必须提供非易失性存储器,以存储FPGA配置流。

REQ4 - 该模块应以方形格式实现。

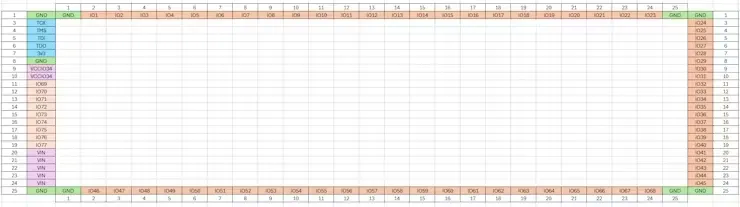

REQ5 - 该模块应在每个方形边缘提供20个I/O(输入/输出)。

REQ6 - 尽可能使用支持差分对的I/O。

REQ7 - 该模块应通过其I/O引脚提供JTAG(联合测试行动组)接口。

REQ8 - 该模块应提供通过USB的编程能力。

REQ9 - FPGA的配置应在NVRAM(非易失性随机存取存储器)和JTAG之间可选择。

REQ10 - 该模块应提供一个25 MHz的振荡器。

REQ11 - 该模块应由5V供电。

REQ12 - 该模块应生成所有必要的内核和I/O电压。

REQ13 - 应提供多个5V输入 - 至少每边一个。

REQ14 - 应提供多个接地 - 至少每边一个。

REQ15 - 连接的间距应允许安装0.1英寸间距的头。

REQ16 - 该模块应至少提供一个用户可访问的LED。

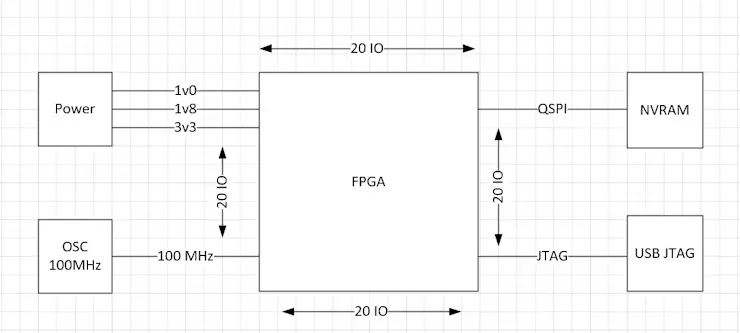

该过程的下一步是创建反映需求的体系结构。电源部分将从板子上获取5V电压,并为FPGA生成内核、辅助和I/O电压。配置数据将存储在NVRAM中,而USB JTAG将为FPGA和NVRAM存储器提供编程能力。预计在USB JTAG和FPGA之间的JTAG输出上,还将连接有头文件,以使用Digilent HS3或Smart Link编程器实现直接JTAG访问。振荡器将是一个标准的100MHz,并将利用内部PLL(锁相环)生成一系列频率。

在专业工程项目中,合规性矩阵是证明解决方案符合要求的方法。

合规性矩阵显示,除了一个需求部分符合外,我们完全符合所有要求。部分符合的情况是因为我们将在模块上提供USB JTAG编程设备;然而,实际的USB连接器将不会在模块上实现。这允许模块的用户根据他们的需求最佳地定位USB连接器。

设计

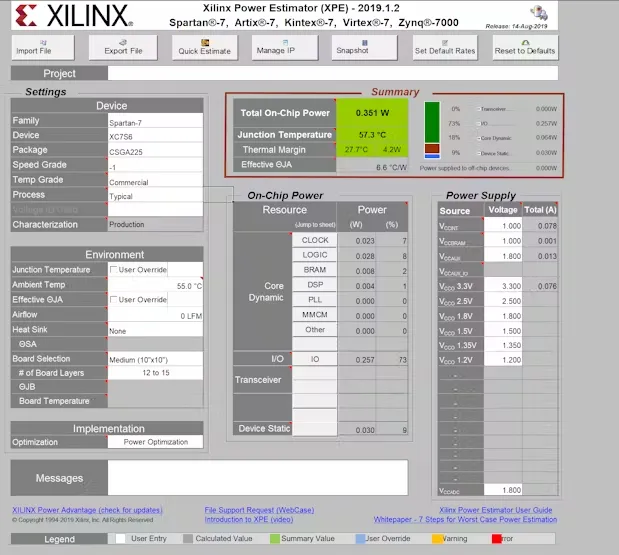

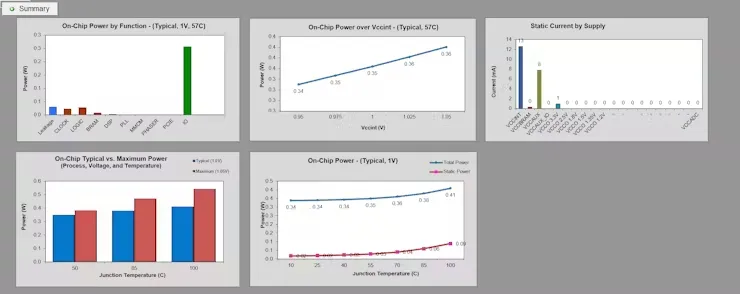

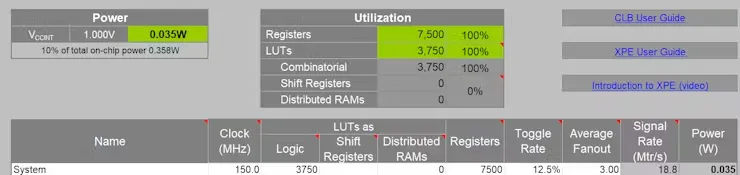

在进入原理图过程之前,需要进行一些设计和分析工作,以确保系统按预期工作。第一步是确保有一个准确的电源估算,这将指导电源设计的尺寸。主要的电源消耗将来自FPGA。因此,需要创建一个准确的功率估算。为此,可以使用 AMD 功耗估算电子表格之一。该工具允许我们定义资源利用率、时钟速率和切换速率,以确定设备的准确功率估计。由于 XC7S6 是可用容量最低的设备,因此这些设备通常具有高利用率。因此,功耗估计将假设 FPGA 的所有资源都已使用。得出的片上总功率估计为 0.351 W。

需要选择其他组件,以便确定它们的功率要求。主要组成部分是FT232H - USB转JTAG芯片93LC56BT - 与FT232H一起使用的JTAG PROMIS25LP256D - 存储配置的FPGA PROM

KC2520Z100.000C15XXK - 100 MHz 振荡器

基线 FPGA 需要 4.3 Mbits 的配置存储器,希望支持 XC7S25 器件,该器件需要 9.9 Mits 的配置数据。因此,选择了 256 Mb QSPI 存储器。这将为开发人员提供实现多重引导和后备解决方案的能力。

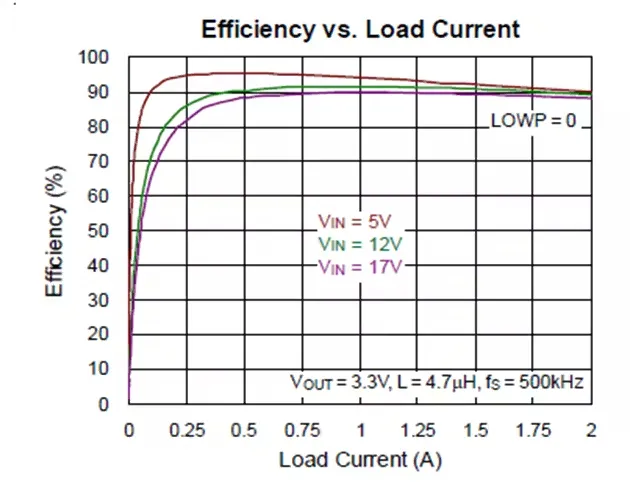

选择FT232H,是因为它是AMD Vivado ™设计套件支持的器件之一,用于通过USB编程以实现USB JTAG功能。确定组件后,下一步是创建整体系统功率预算,以确保电源解决方案的范围正确。选择的功率器件是RICHTEK RT7273GQW,这是一款能够输出 3A 的三路输出开关稳压器,绰绰有余。三通道设计的优势在于它非常紧凑,并且与使用三个分立式电源相比,它支持更小的解决方案。根据 RT7273 的数据手册,需要确定预测效率的最大和最小功率效率以及最坏情况下的负载电流。

必须考虑所选电源开关转换器的效率。

选择组件并确定功耗估算后,我们现在可以开始创建模块的原理图。在选择了组件并确定了功耗估算后,我们现在可以开始为模块创建原理图。

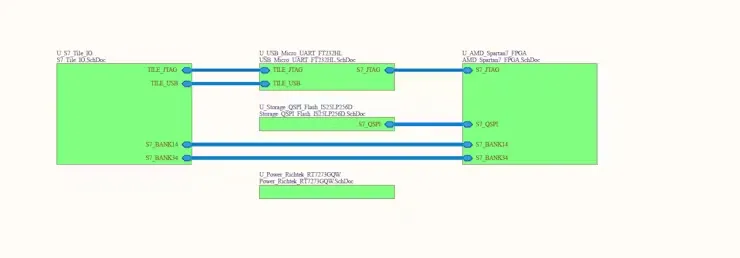

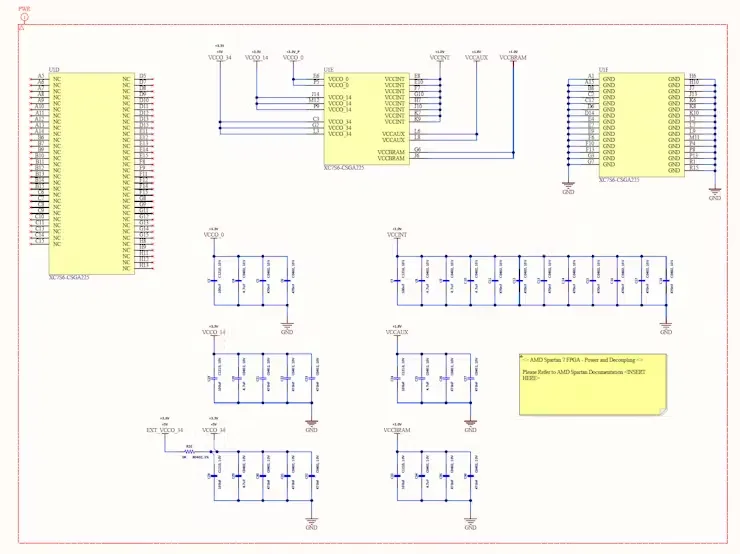

为了创建原理图,我使用了Altium Designer,这是一个我已经拥有了一段时间但最近没有亲自使用过的工具。原理图采用分层设计进行组织,如果需要,可以在多个项目中重复使用。设计要素包括:电源:该模块从输入电压产生 1v0、1v8 和 3v3 电源。NVRAM:此模块包含非易失性配置存储器。FPGA:包含 AMD Spartan 7 XC7S6 设备并断开 I/O。

JTAG:该模块包含FTDI FT4232器件,该器件提供对FPGA的JTAG访问,并对NVRAM进行编程。

为了与我的大多数设计保持一致,我喜欢保持顶层尽可能简单。原理图附在底部的项目上。

电源设计元素概述如下,可生成所需的 1v0、1v8 和 3v3 电压。我在每个输出轨和输入轨上都包含了测试点,并在地面上添加了几个测试点。我的布局计划,是提供两种界面方式。第一种是齿形,可以焊接到电路板的表面贴装。第二个,也是我最有可能用来启动的,是为每个齿形制作一个 0.1 英寸的头部配接孔。因此,对于电源和接地,我为每个引脚添加了五个引脚。一旦我们进入布局阶段,我们就可以将封装修改为所需的形状。

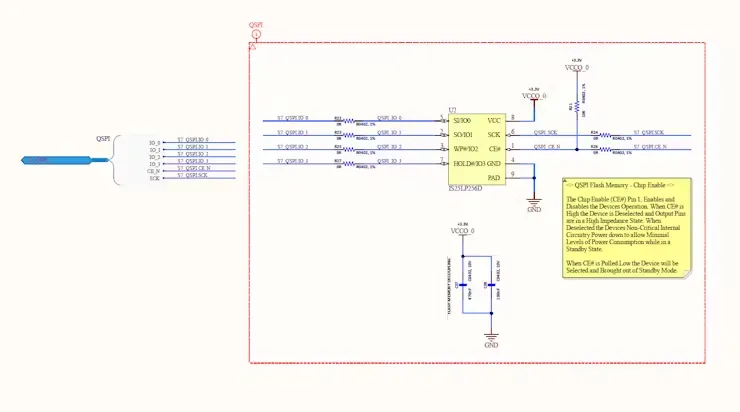

NVRAM 设置非常简单,如下图所示。我添加了上拉电阻器和串联终端电阻器,以备不时之需。

设计中最复杂的部分是FPGA页面。在此页面上,我们将处理配置设置、I/O 分配和电源连接。第一步是根据要求分配模块的外部 I/O。我计划提供JTAG引脚以及VIN和接地。为了提高设计的灵活性,我将允许 BANK 34 使用可选的 I/O 电压,这可以由模块安装的任何设备供电。用户 IO 总数为 77 个 引脚。

为了尽可能简化 FPGA 页面,我将使用分层结构来管理未使用的 I/O 以及电源和接地连接。

为了对设计进行编程,我们需要实现一个JTAG接口。我的计划是使用一个USB和一个通过AMD Vivado编程的FTDI设备。为了保持模块的灵活性,我将不在模块上直接实现USB连接器。取而代之的是,我将把 DP 和 DM 信号分解到边缘齿形。我还计划在边缘齿形上提供JTAG信号。这样做的原因是,如果需要,可以在使用S7 Stamp的系统上创建JTAG链。

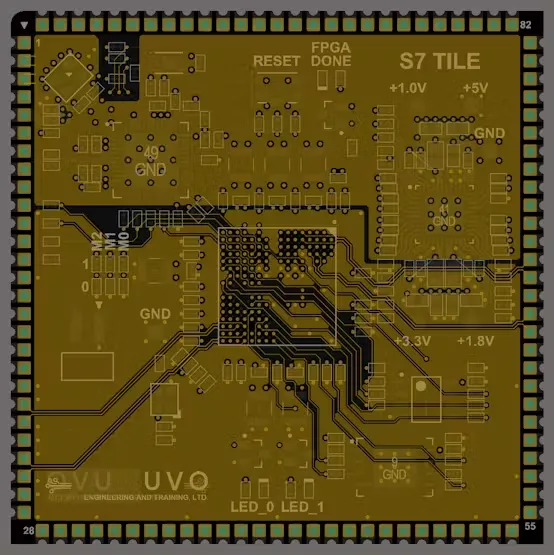

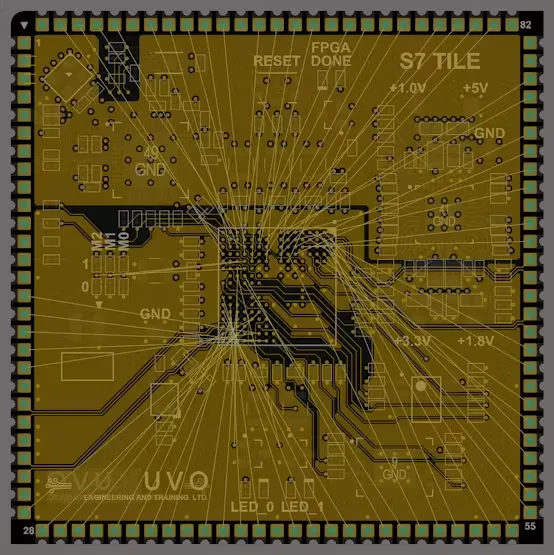

该项目已完成布局,并已开始生产。设计进展中的一些照片可以在下方看到。