时间:2025-02-26 来源:FPGA_UCY 关于我们 0

24.1. 理论学习

IP( )即知识产权。美国咨询公司将半导体产业的IP定义为“用于ASIC或FPGA中的预先设计好的电路功能模块”。简而言之,这里的IP即电路功能模块。IP核在数字电路中常用于比较复杂的功能模块(如FIFO、RAM、FIR滤波器、SDRAM控制器、PCIE接口等)设计成参数可修改的模块,让其他用户可以直接调用这些模块。随着设计规模增大,复杂度提高,使用 IP核可以提高开发效率,减少设计和调试时间,加速开发进程,降低开发成本,是业界的发展趋势。利用IP核设计电子系统,引用方便,修改基本元件的功能容易。具有复杂功能和商业价值的IP核一般具有知识产权,尽管IP核的市场活动还不规范,但是仍有许多集成电路设计公司从事IP核的设计、开发和营销工作。

IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。这种分类主要依据产品交付的方式,而这三种IP内核实现方法也各具特色。

软核是用硬件描述语言的形式功能块的行为,并不涉及用什么电路和电路元件实现这些行为,软IP通常是以硬件描述语言HDL源文件的形式出现,应用开发过程与普通的HDL设计也十分相似,大多数应用于FPGA的IP内核均为软核,软核有助于用户调节参数并增强可复用性。软核通常以加密形式提供,这样实际的 RTL对用户是不可见的,但布局和布线灵活。在这些加密的软核中,如果对内核进行了参数化,那么用户就可通过头文件或图形用户接口(GUI)方便地对参数进行操作。软IP的设计周期短,设计投入少。由于不涉及物理实现,为后续设计留有很大的发挥空间,增大了IP的灵活性和适应性。其主要缺点是在一定程度上使后续工序无法适应整体设计,从而需要一定程度的软IP修正,在性能上也不可能获得全面的优化。由于软核是以源代码的形式提供,尽管源代码可以采用加密方法,但其知识产权保护问题不容忽视。

固核则是软核和硬核的折衷。固核是完成了综合的功能块,有较大的设计深度,以网表的形式交给客户使用。对于那些对时序要求严格的内核(如PCIE接口内核),可预布线特定信号或分配特定的布线资源,以满足时序要求。这些内核可归类为固核,由于内核是预先设计的代码模块,因此这有可能影响包含该内核的整体设计。由于内核的建立时间、保持时间和握手信号都可能是固定的,因此其它电路的设计时都必须考虑与该内核进行正确地接口。如果内核具有固定布局或部分固定的布局,那么这还将影响其它电路的布局。

硬核是完成提供设计的最终阶段产品——掩膜(Mask),以经过完全的布局布线的网表形式提供,这种硬核既具有可预见性,同时还可以针对特定工艺或购买商进行功耗和尺寸上的优化。尽管硬核由于缺乏灵活性而可移植性差,但由于无须提供寄存器转移级(RTL)文件,因而更易于实现IP保护。比如一些FPGA芯片内置的ARM核就是硬核。

同一事物的利弊总是共存的,IP核在拥有以上众多好处的同时也有他的巨大缺点:

1、在跨平台时,IP核往往不通用,需要重新设计。IP核都是不全透明的,是每个FPGA开发厂商根据自己芯片适配的定制IP,所以如果你之前用的的芯片,用了一个PLL,但是因为某些原因需要将代码移植到平台上,那就必须要将PLL给重新替换掉,着增加了代码移植的复杂性。

2、IP核就是个黑匣子,是不透明的,我们往往看不到其核心代码。IP核都是各大FPGA厂商专门设计的,都会进行加密,内核代码都看不到,如果你使用的这个IP核万一出现了问题或者需要知道其内部结构针对具体的应用进行定制优化时,你是无法进行修改的。以上两个问题就很棘手,所以有些公司坚持所有的可综合设计都不使用IP核,就是为了是所有的模块都能够掌控在在自己手里。

3、有些定制的IP核由于是不通用的,往往会有较高的收费,这也是一笔巨大的开销。所以IP核在能够加快我们开发周期的情况下也存在以上三种常见的问题,这就是需要我们权衡利弊,针对具体的需求来做具体的选择。

从软 IP 到硬 IP,设计灵活性降低,设计深度提高,设计成功率提高。公司提供两类功能模块:免费的LPM宏功能模块(/LPM)和需要授权使用的IP知识产权(),两者的实现功能上有区别,使用方法相同。从复杂性的角度看,支持系列FPGA的IP核既包括注入逻辑和算术运算等简单的IP核,也包括诸如数字信号处理器、以太网MAC、PCI/PCI 接口等比较复杂的系统级构造模块。按其功能划分, IP核主要有以下几类:

1、逻辑运算IP核。包括与、或、非、异或等基本逻辑运算单元和复用器、循环移位器、三态缓存器和解码器等相对复杂的逻辑运算模块。

2、数学运算IP核。的数学运算IP核分为整数运算和浮点运算两大类:(1)整数运算IP核。包括LPM库(参数化模型IP库)提供的IP核和指定功能的IP核。LPM库中的IP核有加法器、减法器、乘法器、除法器、比较器、计数器和绝对值计算器;指定功能的IP核包括累加器、ECC编码器/解码器、乘加器、基于存储的常系数乘法器、乘累加器、乘加器、复数乘法器和整数平方根计算器等。(2)浮点运算IP核包括浮点数加法器、浮点数减法器、浮点数乘法器、浮点数除法器、浮点数平方根计算器、浮点数指数计算器、浮点数倒数计算器、浮点数平方根倒数计算器、浮点数自然对数计算器、浮点数正弦余弦计算器和反正切计数器、浮点数矩阵求逆和乘法器以及浮点数绝对值计算器、比较器和转换器等。

3、存储器类IP核。包括移位奇存器、触发器、锁存器等简单的存储器IP核和较为复杂的ROM、RAM、FIFO和Flash存储器等模块。另外,还提供了包括RAM初始化器和针对部分FPGA系列应用的FIFO分割器等辅助存储器设计IP核。

4、数字信号处理IP核。包括有限冲激响应滤波(FIR)编译器、级联积分梳状(CIC)滤波器编译器、数控振荡器(NCO)编译器以及快速傅里叶交换(FFT)等IP核,用于数字信号系统设计。

5、数字通信IP核包括RS码编通器、用于ひ积码译码的译码器、循环冗余校验(CRC)编译器、8B/10B编/译码器以及SONET/SDH物理层IP核等。

6、图像处理IP核。主要是实现视频和图像处理系统中常用功能的IP核,具体有2DFIR滤波器和2D中值滤波器、α混合器、视频监视器、色度重采样器、图像裁剪器、视频输入和输出模块、颜色面板序列器、颜色空间转換器、同步器、视频帧读取和缓存器、γ校正器、隔行扫描和去隔行扫描器、缩放器、切换器、测试模板生成器和视频跟踪系统模块。

7、输入/输出P核。主要包括时钟控制器、锁相环(PLL)、低电压差分信号(LVDS)收发器、双数据速率(DDR)I/O、访问外部存储器的DQ-DQS I/O、I/O缓存器等。

8、芯片接口IP核。包括用于数字视频广播(DVB)的异步串行接口(AS1)、10/100/以太网接口、DDR和DDR2 SDRAM控制器、存储器物理层访问接口、PCI/PCI 编译器、和用于数字电视信号传输的串行数字接口(SDI)等。

9、设计调试IP核。包括提供设计调试功能的逻辑分析仪、串行和并行Flash加载器、系统内的源和探测模块以及虚拟JTAG等。

10、其他IP核。还有一些针对部分系列FPGA应用的专用IP核,这里不再一一列举。

本章将重点介绍几个常用的IP,如锁相环(PLL)、FIFO、RAM、ROM等,详细说明各IP核的功能以及其使用方法,通过使用这些简单的IP核来掌握所有IP核的基本使用方法,起到抛砖引玉的效果。

IP核可以通过 II软件集成的插件管理器、SOPC构造器或DSP构造器、Qsys设计系统例化,后两者仅支持部分IP核的例化和使用,非的第三方IP核以网表文件方式提供。本章主要介绍在插件管理器定制和例化 IP核的方法。

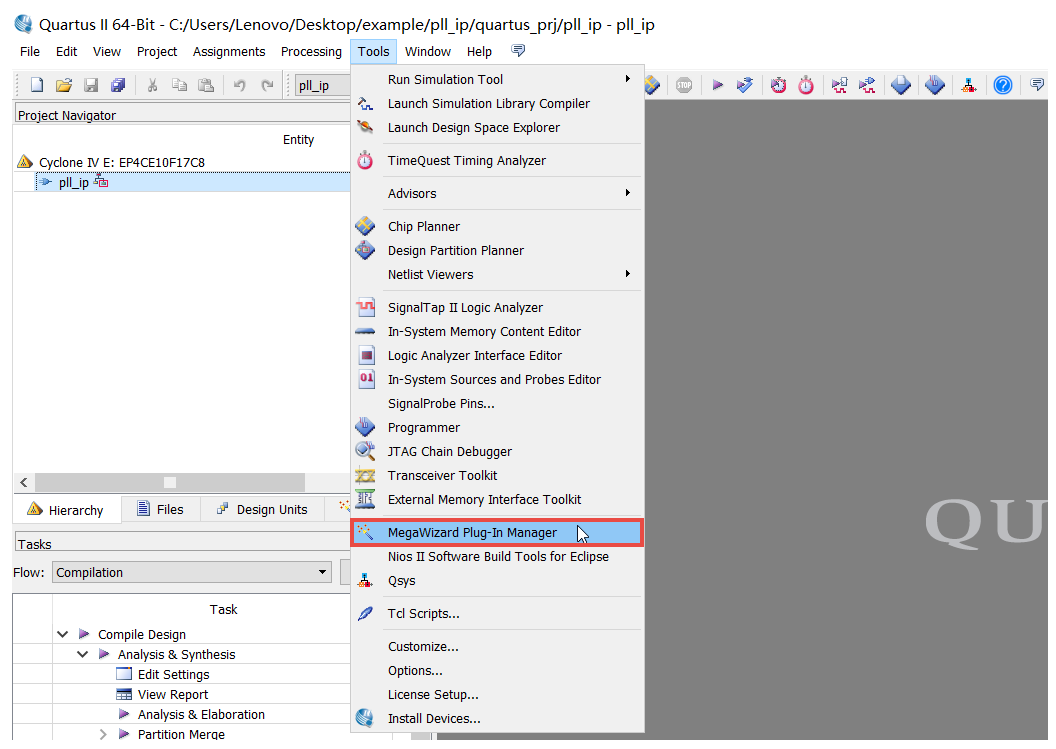

插件管理器可以用于创建和修改包含定制IP核的设计文件,然后在设计文件中例化IP核。在插件管理中可以创建、定制和例化 IP核、参数化模型库(LPM)模块以及在 II软件、EDA设计入口和综合工具使用的IP核。插件管理器自动生成可以在VHDL设计文件(.vhd)中使用的组件声明文件(.cmp)以及可以在文本设计文件(.tfd)和设计文件(.v)中使用的AHDL包食文件(.inc)。还为AHDL设计、VHDL设计和设计生成后级名分别为“_inst.tdf”、“_inst.vhd”和“_inst.v”的例化模板文件。此外,插件管理器还为设计创建例化声明文件,文件后级为“_bb.v”。例化文件包含定制IP核的模型和端口声明。使用插件管理器可以指定IP核的不同选项,包括设置参数值和选择可选端口,还可以为第三方综合工具生成网表文件。如图 30‑1所示,我们点击“Tools”目录下的“-In ”打开插件管理器。

图 30‑1 创建IP核步骤(一)

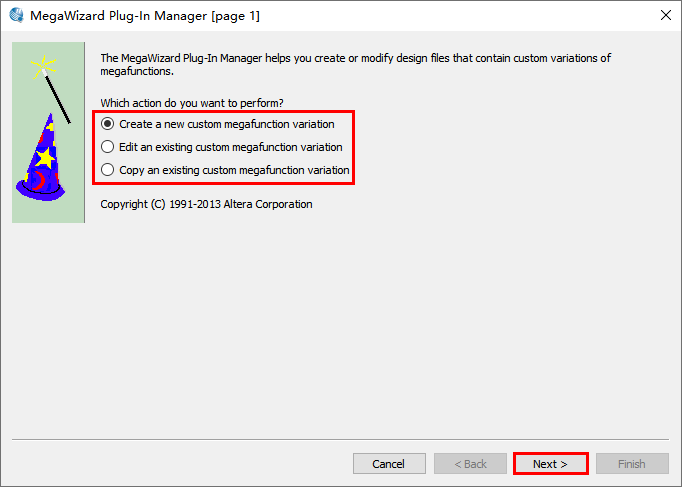

如图 30‑2所示的框,如果创建一个新的IP核选择第一个“ a new ”,如果编译已存在的IP核选择第二个“Edit an n”,如果复制已存在的IP核选择第三个“Copy an ”,选择后点击“Next”。

图 30‑2 创建IP核步骤(二)

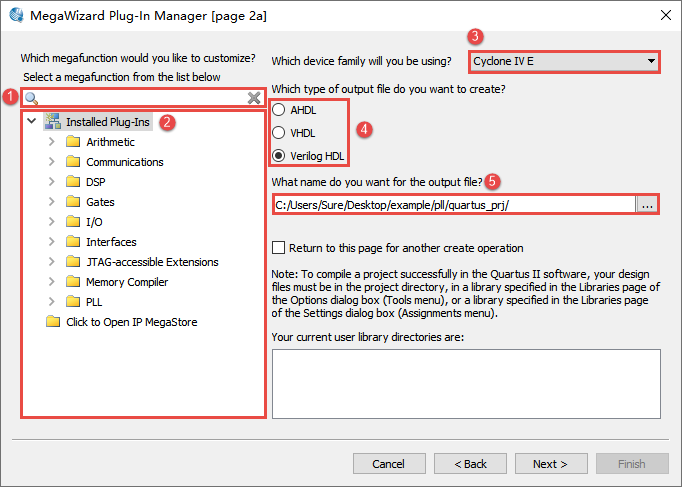

如图 30‑3所示,在打开的界面由以下几个主要部分组成:

框 1 提供了一个搜索框,可以通过 IP 核名称来搜索。

框 2 为 IP 核列表, 提供的 IP 核都列在其中,每个文件夹代表一类,比如 里包含了与存储器有关的 IP 核。

框 3为工程指定的 FPGA 所属的器件系列,每个器件系列能提供的 IP 核种类与数量不尽相同,所以这个地方要保持与工程创建时选择的器件系列一致,避免出现添加本器件不支持的情况,这里默认是一致的。

框 4为添加 IP核时输出文件的语言类型,这个取决于工程具体设计所使用的语言,这里选择 。

框 5 是 IP 核输出文件的保存类型及 IP 核名称,路径一般在工程文件夹中。

图 30‑3 创建IP核步骤(三)