时间:2025-01-26 来源:FPGA_UCY 关于我们 0

一、FPGA开发流程

1、设计定义:设计的目标系统需要完成什么样的功能进行定义。俗称“画饼”。

2、设计输入:设计开始,首先利用EDA工具的文本或者图形编辑器将设计者的设计意图用文本方式(如、VHDL程序)或者图形方式(原理图、状态图等)表达出来。虽然原理图输入方式所画的的原理图与传统的器件连接方式完全一样,很容易被人们所接受,而且编辑器中也有很多现成的单元器件可资利用,自己也可以根据需要设计元件(元件的功能可用HDL程序表达,也可以用原理图表达)。当然最一般化、最具普适性的输入方式是HDL程序的文本方式。这种方式与传统的计算机软件语言编辑输入基本一致。目前有些EDA工具可以把两种输入方式的优势结合起来,实现效率更高的输入。

3、分析与综合:一般由编译软件完成,主要检查设计输入的程序是否有语法和逻辑错误。所谓综合就是将较高级抽象层次的描述转化成较低层次的描述。

4、功能仿真:直接对、原理图描述或者其他描述形式的逻辑功能进行测试模拟,以了解其实现的功能是否满足原设计要求的过程,仿真过程不涉及任何器件的硬件特性。

5、布局布线:将综合生成的逻辑网表配置到具体的FPGA芯片上,布局将逻辑网表中的硬件原语和底层单元合理地配置到芯片内部的固有硬件结构上,并且往往需要在速度最优和面积最优之间作出选择。布线根据布局的拓扑结构,利用芯片内部的各种连线资源,合理正确地连接各个元件。

6、时序仿真:接近真实器件运行特性的仿真,仿真文件中已包含器件硬件特性参数,因而仿真精度高。但时序仿真的仿真文件必须来自针对具体器件的综合器与适配器。-----当时序仿真不通过时候,首先可以考虑改变设计输入或者进行时序约束。

7、IO分配以及配置文件的生成:分配管脚和生成配置文件。

8、配置(烧写FPGA文件):-----FPGA配置方式主要有主动串行方式(AS)、主动并行(AP)、被动串行方式(PS)、快速被动并行(FPP)和最常用的JTAG配置方式。

9、在线调试:在线调试方法–信号探针()、在线逻辑分析仪( II Logic )、逻辑分析仪接口(Logic )、在线存储内容编辑(In- )、例化一个定制的寄存器链到 FPGA 器件内部(In- and )。

二、适用的设计

适用:系统级、算法级、寄存器传输级(RTL)、逻辑级别、门级、电路开发级。其中系统级、算法级、寄存器传输级(RTL)属于行为描述。只有RTL级才有与逻辑电路有明确的对应关系。

三、示例实录

1、设计定义:实现二选一多路选择器。给定两路输入信号a和b,通过按键开关实现开关按下时候输出为a的值,按键松开时候输出值为b的值。

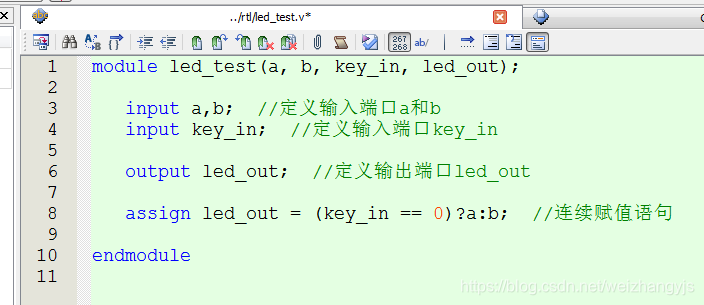

2、设计输入:采用HDL程序设计方式。 建立工程,新建程序编辑文本文件。编写HDL文件。

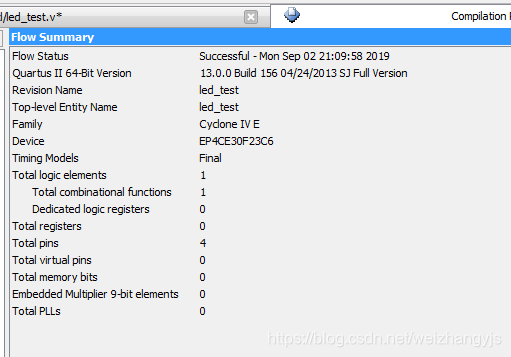

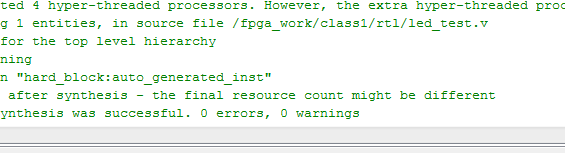

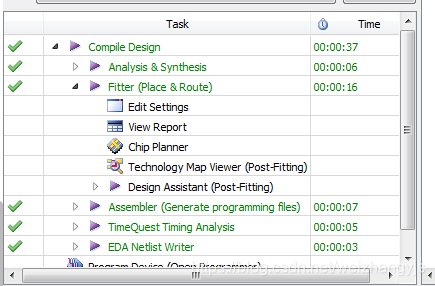

3、分析与综合:

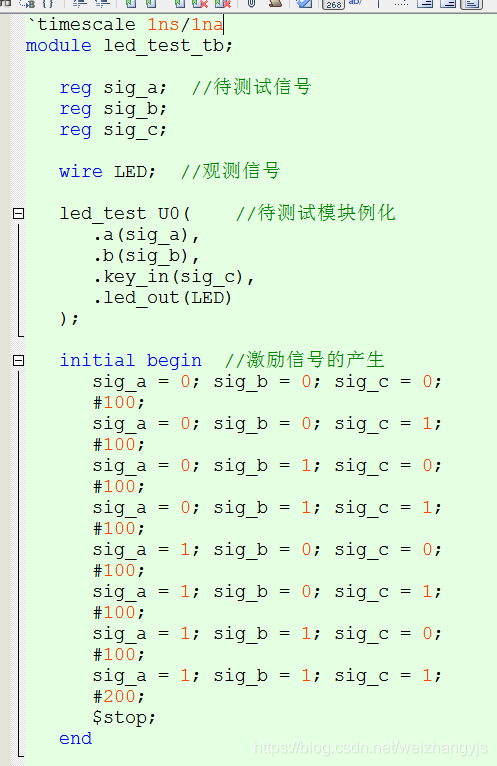

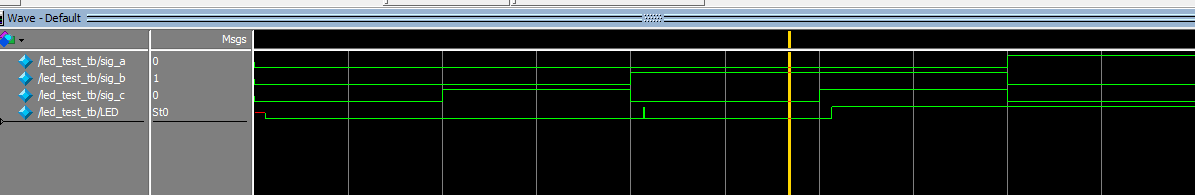

4、功能仿真:

5、布局布线:由编译器完成。

6、时序仿真:产生了实际电路的存在的毛刺信号和传输延时现象。

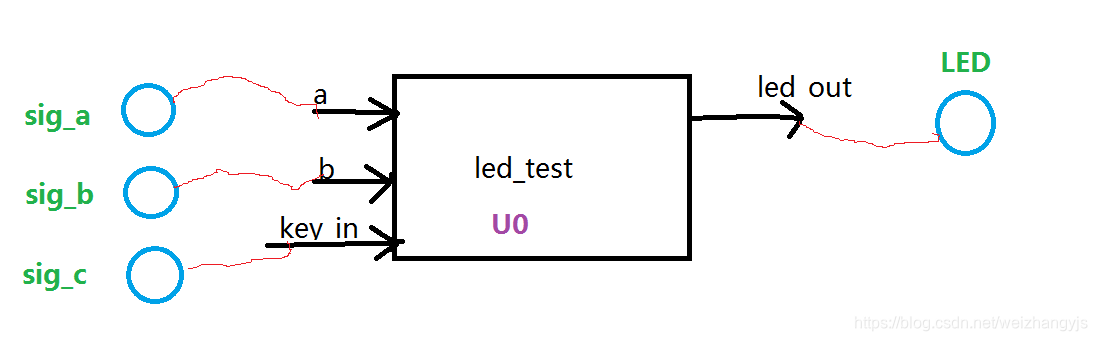

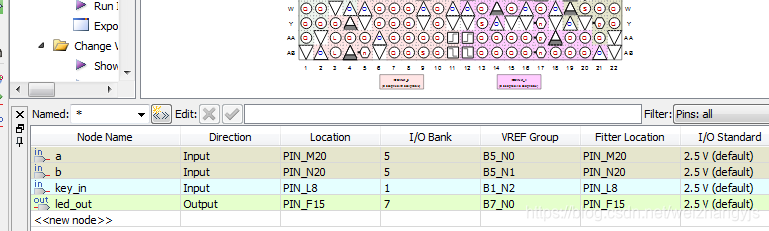

7、IO分配以及配置文件生成:

8、配置(烧写程序)。

9、实验部分。