时间:2024-08-08 来源:网络搜集 关于我们 0

系统整理一下关于赛灵思FPGA原理图的设计过程,一方面记录下,另一方面小伙伴沟通交流。之前提到了一下FPGA启动配置过程。本篇介绍FFVA1156 (XCKU040)器件时钟源、交代下文档路径:赛灵思官网-->产品-->FPGA-->UltraScaleFPGA选型手册-->ug572文档

在原理图设计时,这一块需要FPGA工程师验证仿真成功后再开展工作。本案仅站在硬件原理图的角度上来分析,毕竟不是FPGA工程师涉及内部时钟分配和实现不做介绍。整体来看就是FPGA内部集成了一个时钟发生器,支持锁相、倍频、分频、相移、去抖动、开展频、巴拉巴拉的一大堆。。。。。

硬件涉及时钟的PIN如下:

CMT介绍:包括一个混合模式时钟管理器(MMCM)和两个锁相循环(PLLs)、主要功能就是产生时钟。

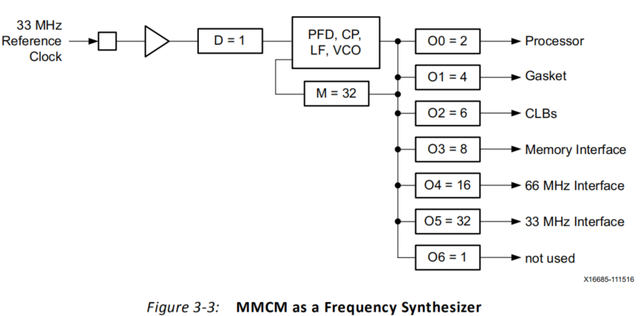

1、如下MMCM拓扑,它支持多个参考时钟输入,后级经过鉴相器PFD、电流泵CP、滤波器LF、晶振VCO、分频器后输出、且可以调整相位。

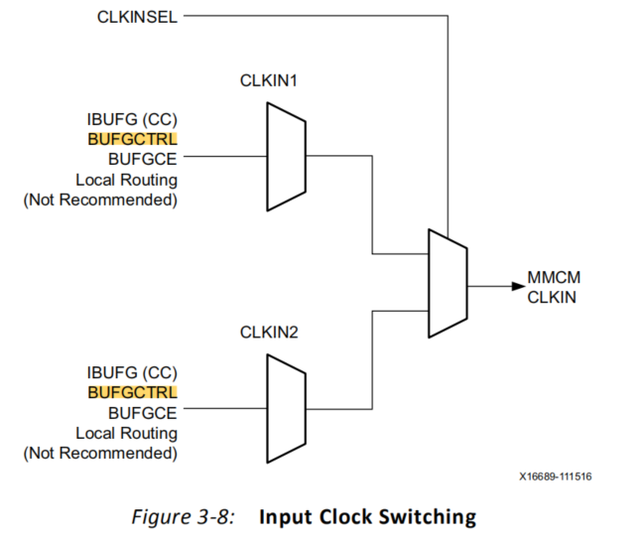

其输入源:IBUFG (CC)、BUFGCTRL、BUFGCE、Local Routing如下所示,其中CC通GC引脚、BUFGCTRL、BUFGCE为GC的buff。一版采用GC作为其输入参考时钟。

参数计算如下:

其中根据ds892文档得知Fvco范围:600MHz-1440MHz、MMCM输入时钟范围:10-00MHz (VCCINT:-1速度等级下),根据合理的设置M,D,O参数即可获得相应频率的时钟,下面提到了一个例子。

另外输出相位移动调整、参考输入时钟如何切换、输出要不要加buff,要不要开展频啊、一句话:参数代码可配不涉及硬件的功能本案暂不做介绍。

2、每个CMT中都有两个PLL为PHY逻辑和IO提供时钟。它们可以用作广泛频率范围的频率合成器,作为抖动滤波器,并提供基本的相移能力和占空比编程,它没有先进的相位移动且相应的参数设置有限为专用的存储器接口电路提供必要的时钟的、简单的说就是阉割版本的MMCM不做过多介绍了。

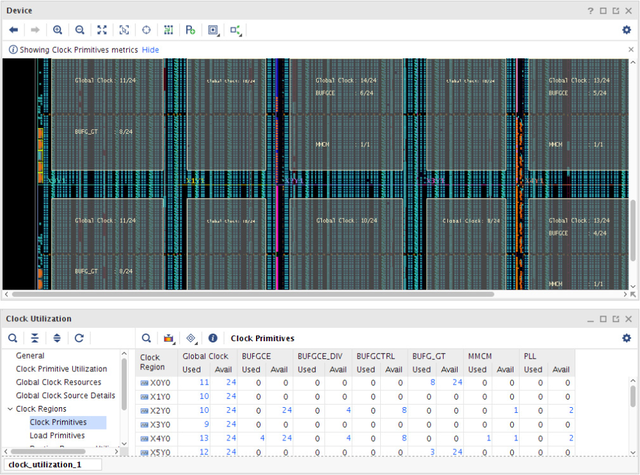

Vivado Design Suite features也提供了一下时钟设置工具,可以通过IP Catalog中提供的Clocking Wizard来选择并配置MMCM和PLL。巴拉巴拉的,硬件的我选择视而不见,ok先到这吧。