大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资源,或者一起煮酒言欢。

今天给大侠带来“FPGA学习系列 altera"系列,持续更新。此学习心得是本人之前所写,所用设计软件为Quartus II 13.1,现Quartus 新版本已更新到20+,以下仅供初学者学习参考。后续会更新其他系列,敬请关注。话不多说,上货。

下板驱动安装

分配完管脚后,要进行全编译,这里我就直接点击快捷键了,如下,不熟练的小伙伴们可以自己从最上面的操作栏自己选。 形成配置文件(sof文件、pof文件)。Altera 芯片去下载配置文件需要安装驱动,已经安装的小伙伴可以自动略过。1. 将下载线的组装好。一般都是有usb线、下载器和一段“排线”构成。2. 将usb插口插入电脑usb接口,将“排线”插入开发板的jtag口(开发板不上电)。3. 右击‘我的电脑’打开设备管理器。

形成配置文件(sof文件、pof文件)。Altera 芯片去下载配置文件需要安装驱动,已经安装的小伙伴可以自动略过。1. 将下载线的组装好。一般都是有usb线、下载器和一段“排线”构成。2. 将usb插口插入电脑usb接口,将“排线”插入开发板的jtag口(开发板不上电)。3. 右击‘我的电脑’打开设备管理器。 4. 右击USB-blaster ,选择‘更新驱动程序’。

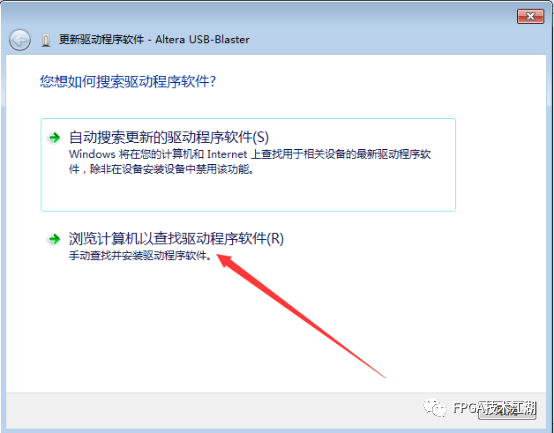

4. 右击USB-blaster ,选择‘更新驱动程序’。 5. 点击‘浏览计算机以查找驱动程序软件’。

5. 点击‘浏览计算机以查找驱动程序软件’。

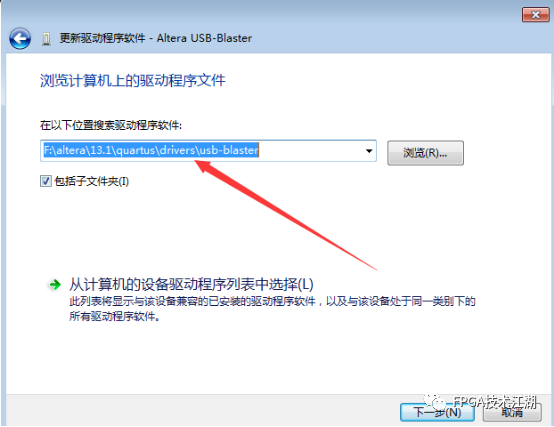

6. 点击浏览。

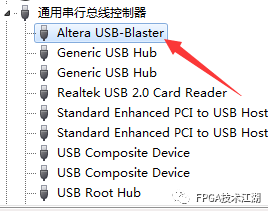

7. 按照笔者给大家提供的路径,大家可以去自己安装的盘符中寻找这个路径(在usb-blaster文件下,有x64和x32,不要去选,直接选择usb-blaster就好了)。8. 点击下一步,完成安装(有电脑会提示是否安装,点击安装或者允许)。9. 查看设备管理器中,通用串行总线控制器中多了一个altera USB-blaster。

至此,我们完成了驱动的安装。下载驱动只需要安装一次,后面我们就可以无限次下载配置文件了。下载配置文件

将下载线(USB-blaster)一端连接到JTAG口,一端连接到电脑上,下面我们就可以下载配置文件了。1. 打开配置界面。1) 点击。

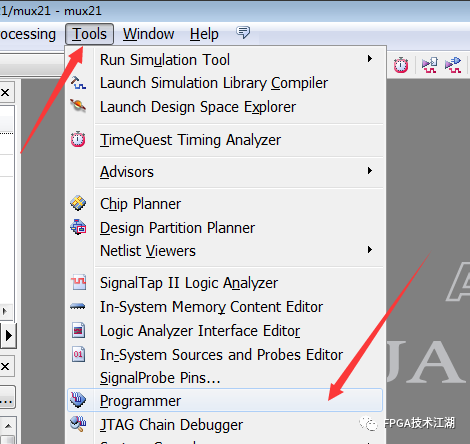

2) 点击Tools->Programmer.

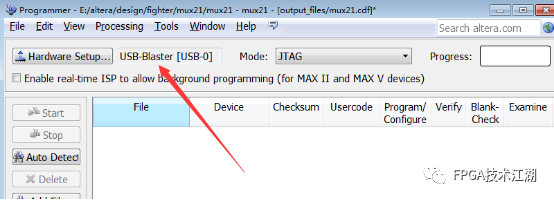

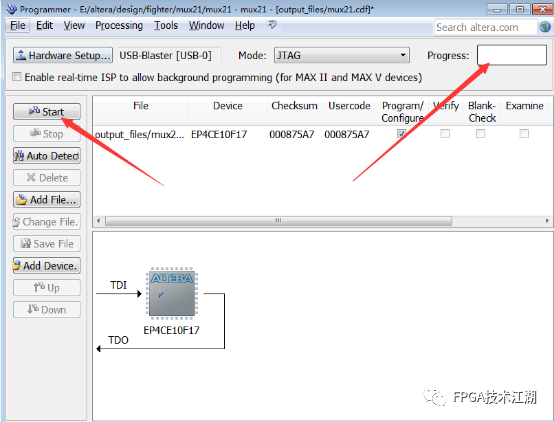

3) 下载配置界面如下:

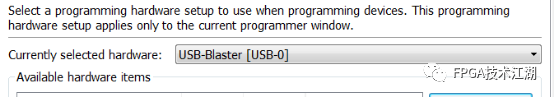

2. 点击Hardware Setup ,界面如下: 3. 点击No Hardware ,选择usb-blaster,然后点击Close。1) 点击No Hardware。

3. 点击No Hardware ,选择usb-blaster,然后点击Close。1) 点击No Hardware。

2) 选择usb-blaster。

3) 点击Close。

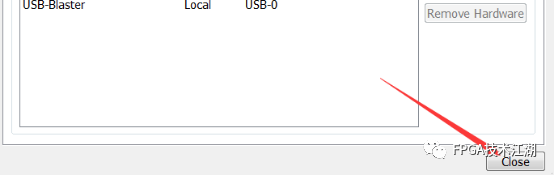

4. 成功选择USB-blaster,界面如下:

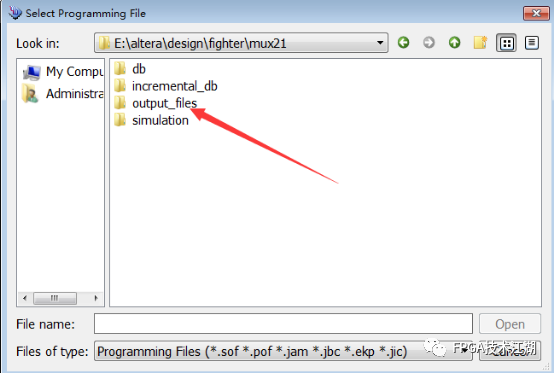

5. 添加配置文件。1) 点击add file。 2) 打开output_files。

2) 打开output_files。

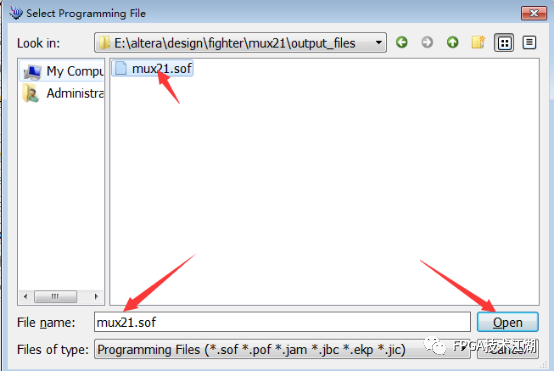

3) 选中sof文件,点击open。

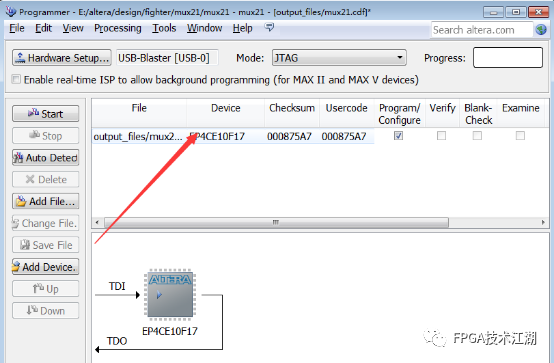

4) 添加成功以后的界面。

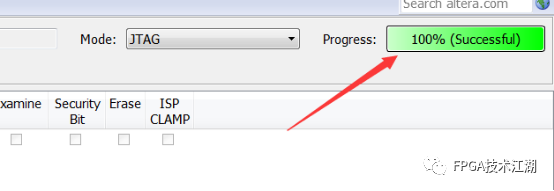

6. 点击Start,观察右上方进度,当100%后就成功了。

7. 下载成功,界面如下:

下板之后,如果开发板的运行情况和我们所设计的不一样的话,我们应该去检查我们的设计,检测问题的所在,然后重新下板。至此我们完成了一个设计中的所有的步骤,任何设计我们都应该遵循这个设计过程。

- THE END -

🍁

往期精选

【免费】FPGA工程师人才招聘平台

FPGA人才招聘,企业HR,看过来!

系统设计精选 | 基于FPGA的实时图像边缘检测系统设计(附代码)

基于原语的千兆以太网RGMII接口设计

时序分析理论和timequest使用_中文电子版

求职面试 | FPGA或IC面试题最新汇总篇

资料汇总|FPGA软件安装包、书籍、源码、技术文档…(2024.01.06更新)

FPGA就业班,05.04开班,新增课程内容不加价,高薪就业,线上线下同步!

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+学校/公司+专业/岗位进群

FPGA技术江湖QQ交流群

备注姓名+学校/公司+专业/岗位进群

注明:本内容来源网络,不用于商业使用,禁止转载,如有侵权,请来信到邮箱:429562386ⓐqq.com 或联系本站客服处理,感谢配合!