时间:2024-07-26 来源:网络搜集 关于我们 0

一、为什么要换个姿势学FPGA?

大家好,我是杜勇,一名资深FPGA数字信号处理算法工程师,一名高校教师,也是一名UP主,业余时间喜欢看球赛、看电影、听音乐、看书,慢跑,感觉快乐的生活状态是一边看球赛、一边喝茶、一边等待FPGA程序的运行结果。

在经过多年的FPGA工程项目设计之后,感慨于当初学习相关技术时找不到可用参考资料(主要是工程实现方面的可用资料缺乏)的无助,抱着减少后来者踩坑迷茫的微小愿望,又机缘巧合,刚好有一段较长的相对空闲的时间,于是开始编写《数字滤波器的MATLAB与FPGA实现》等数字信号处理的系列图书。蓦然回一下首,已是11年前,2012年。后来陆续出版通信同步、调制解调、锁相环技术、数字信号处理设计等FPGA设计与实现的图书。

很幸运,二十余年来一直在从事FPGA设计相关的工作,亲身感受到FPGA技术的发展已成汪洋之势。

但是,很多人说,入门难!

目前很多高校从本科开始开设FPGA课程,并且越来越多的学校开始将传统的《数字电路技术》课程与FPGA技术课程融合起来讲解。FPGA技术入门难,但其发展趋势已不可逆转,一些课堂在认真细致的讲解繁杂的Verilog HDL语法时,且因语法与C语言长得相似,而宽慰学生那颗对硬件描述语言的畏难之心。

数字电路技术中组合逻辑简单直接,很容易上手,但令学生头疼的是随之而来的时序逻辑设计,尤其是状态方程的分析理解。解方程?这与数学问题好相似!然而,更难的还在后面,要用不太熟悉的状态机描述不太熟悉的时序逻辑电路。老师,这种功能的电路要分成几个状态呢?如何画状态转移图呢?学生在经历了短暂愉快的组合逻辑电路设计之后,很快就遭遇到时序逻辑设计的无情阻碍。

再用Verilog HDL语言,按照已训练成熟的C语言思维描述硬件电路,再次经历学习的迷茫。请问“=”和“<=”到底有什么区别?为什么叫阻塞赋值?为什么叫非阻塞赋值?什么叫立即执行,什么叫顺序执行?“=”和“<=”什么时候相同,什么时候不同?为什么C语言可以这样写,Verilog HDL就不行?

或许,我们可以换个思路学FPGA!

需要理解Verilog HDL的本质是并行语言,C语言是顺序语言,他们俩除长得像以外,也就仅仅是长得像而已!理解了D触发器的时序波形,再用并行语言的思维去理解“=”和“<=”,就一切清晰明了,豁然开朗。

所谓时序,就是时间的先后关系,在时钟的驱动下计数,就可以生成各种与时间相关的信号。设计时序逻辑,本质是设计计数器而已。计数器,谁还掌握不了呢?

或许,我们可以换个姿势学FPGA!

暂时放下状态机的概念、放下对顺序语言思维的执着,按照数字电路的工作方法,从D触发器、计数器入手,详细阐述并行语言的精髓,打通硬件描述语言的学习关卡,跨入FPGA技术的大门。

《零基础学FPGA设计——理解硬件编程思想》是我于2023年4月由电子工业出版社出版的图书,专为FPGA初学者编著,希望能够帮助大家快速跨入FPGA技术的门槛。

二、为什么要用国产FPGA?

近年来,国际国内的芯片产业正经历大的变革时期。AMD和Intel两家的FPGA仍然占据全球FPGA的绝大部分市场,但你经历过买不到芯片的困境吗?或者经历过设计好的开发板,在要量产时,供货商的价格傲娇到高攀不起的情况?

更重要的是,或许正是由于米国的一顿凶猛操作,国产芯片的崛起已是大势所趋,不可阻挡。作为一名长期从事FPGA设计的从业者,明显体会到近年来采用国产FPGA开发的项目越发呈快速增长之势。

又是机缘巧合,刚好,有机会和高云FPGA合作,推出国产FPGA开发平台的入门级图书。

坦诚来讲,高云的云源软件,以及其它国产FPGA开发软件,与ISE、Vivado、Quartus相比还存在明显的差距,但这主要体现在高阶的应用方面。对于初学者来讲,国产FPGA开发环境却反而友好得不是一点点,是很多很多。从安装过程到使用步骤都更具亲和力,初学者反而不用为学习繁杂的开发工具使用方法花费过多的时间。而学习FPGA的核心,一定是理解硬件编程思想,掌握硬件编程方法。开发环境的使用大同小异。相信我,相信成千上万的FPGA开发工程师的切身体会,在你熟悉FPGA开发方法后,学习其它开发环境一定是一件轻松惬意的事。就正如,如果你掌握了Verilog HDL语言,即使从未编写过VHDL代码,人生第一次看见一段VHDL代码也会感到无比的亲切。因为,他们并没有本质上的不同。

三、确认视频是完备的?认真录制的?完全免费的?

是完备的,是认真录制的,是完全免费的。我于2022底~2023年初完成了42集配套视频的录制,已在B站(UP主:杜勇FPGA)发布完毕。在你观看视频的过程中,或许会感觉到有几期视频的声音有一点特别,就是有点沙哑,好像感冒了?或许你已经猜到了。在那场席卷全球的疫情面前,我也荣幸的经历了一次洗礼。

春回大地,万物复苏。五一节的人海,让那场疫情恍如隔世!

四、章节编排的理由

全书分四篇:基础篇、初识篇、入门篇和提高篇。

基础篇中只用一章的篇幅介绍与FPGA设计相关的,数字电路课程的核心内容,另外二章讨论逻辑电路基础知识和环境安装方法。

初识篇先用流水灯电路体验FPGA的开发流程,你会发现其实比想象中简单很多,尤其采用云源软件开发时。再多角度阐述D触发器这个灵魂,和计数器这个精华。这两个简单的内容讲得太多了吗?不,不,不。根据“换个姿势”的出发点,编写FPGA程序不过是反复写D触发器和计数器而已,无论是后面讲的秒表电路、串口电路、还是音乐放器,莫不如此。在讲D触发器和计数器时,注意融合FPGA并行设计思想,简洁明了彻底理解“=”“<=”等与C语言截然不同的概念。

入门篇就开始起飞了。秒表电路几乎人人都在设计,网上充斥很多学习的代码。什么样的代码才是简洁、美观的呢?如果你发现了和书中类似风格的代码,如果代码是在2019年以前发布的(我于2019年通过开发板发布了秒表、按键消抖、串口通信这类基础代码),只能说发布者和我的审美相差无几吧,如果全都是2019年后发布的,希望大家能够在使用的时候注明出处啊。密码锁、电子琴电路的设计问题,已初步超越了FPGA语法的范围,其实只是训练学习者的逻辑思维能力罢了。串口通信是一个应用非常广泛的功能电路。经常看到学生从网上找到用状态机写的串口代码。为什么要用状态机呢?用计数器的方法无论从理解的角度,还是实现的角度都更为简单清晰。虽然不提倡用状态机的思路写代码,但还是用一章的内容对此进行了讨论,并以序列检测器的程序为例进行了对比分析。用D触发器的思想写序列检测器是多么多么的简单啊!

提高篇讨论了时序约束、IP核设计、在线逻辑分析仪和常用设计技巧。其实在经历过前面三篇的学习之后,如果初学者已经能够在不参考任何代码的前提下,从头开始写完整个的“串口控制秒表电路”,相信已经基本跨入了FPGA设计的大门,已经具备顺利自学这一篇内容的条件和能力了。

五、学无止境

没有一本书能够把FPGA设计的方方面面都讲到,通过学习一本书就能完全掌握FPGA设计的所有技巧只是一个美好的愿望而已。熟练的应用需要学习者大量的练习和思考。《零基础学FPGA设计——理解硬件编程思想》只是采用另一种姿势,给大家提供另一种学习的方法,帮助大家快速、顺利的跨入FPGA设计的大门而已。

一定要有CGD100开发板,一定要用云源软件才能使用这本书吗?不,不,不。

重要的事说三篇:开发环境是次要的,核心是理解硬件编程思想,思想,思想!

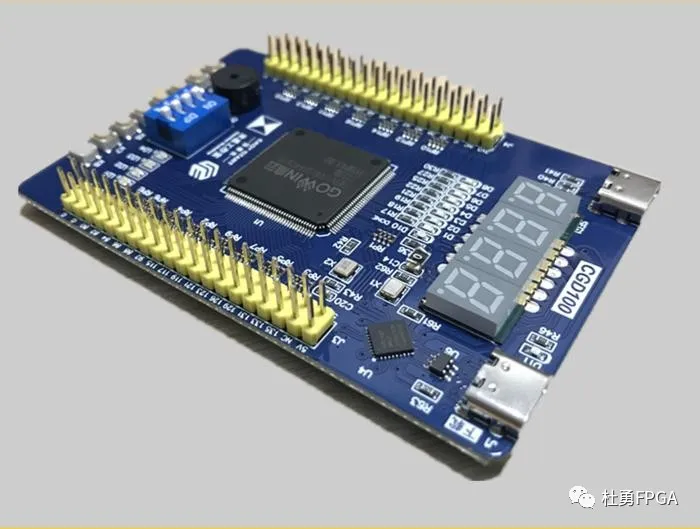

图书配套开发板CGD100实物图

六、图书目录

第一篇 基础篇

第 1 章 必备的数字逻辑电路知识

第 2 章 可编程逻辑器件基础

第 3 章 准备好设计环境

第二篇 初识篇

第 4 章 FPGA 设计流程—LED 流水灯电路

第 5 章 从组合逻辑电路学起

5.1 从最简单的与非门电路开始

5.1.1 调用门级结构描述与非门

5.1.2 二合一的命名原则

5.1.3 用门级电路搭建一个投票电路

5.2 设计复杂一点的投票电路

5.2.1 门电路设计方法的短板

5.2.2 assign 语句完成门电路功能

5.2.3 最常用的 if-else 语句

5.2.4 reg 与 wire 的用法区别

5.2.5 记住“<=”与“=”赋值的规则

5.2.6 非常重要的概念——信号位宽

5.2.7 行为级建模的 5 人投票电路

5.3 ModelSim 仿真电路功能

5.3.1 4 线-2 线编码器设计

5.3.2 建立 ModelSim 工程

5.3.3 设计测试激励文件

5.3.4 查看 ModelSim 仿真波形

5.4 典型组合逻辑电路 Verilog HDL 设计

5.4.1 8421BCD 编码器电路

5.4.2 8 线-3 线优先编码器电路

5.4.3 74LS138 译码器电路

5.4.4 与 if-else 齐名的 case 语句

5.4.5 数据分配器与选择器电路

5.5 数码管静态显示电路设计

5.5.1 数码管的基本工作原理

5.5.2 实例需求及电路原理分析

5.5.3 数码管显示电路 Verilog HDL 设计

5.5.4 板载测试

第 6 章 时序逻辑电路的灵魂——D 触发器

6.1 深入理解 D 触发器

6.1.1 D 触发器产生一个时钟周期的延时

6.1.2 D 触发器能工作的最高时钟频率

6.2 D 触发器的描述方法

6.2.1 单个触发器 Verilog HDL 设计

6.2.2 带异步复位信号的 D 触发器

6.2.3 带同步复位信号的 D 触发器

6.2.4 带时钟使能信号的 D 触发器

6.2.5 D 触发器的 ModelSim 仿真

6.2.6 其它形式的 D 触发器

6.3 初试牛刀—边沿检测电路设计

6.3.1 边沿检测的功能描述

6.3.2 边沿检测电路的 Verilog HDL 设计

6.3.3 改进的边沿检测电路

6.4 连续序列检测器——边沿检测电路的升级

6.4.1 连续序列检测电路设计

6.4.2 分析 Verilog HDL 并行语句

6.4.3 再论“<=”与“=”赋值

6.4.4 序列检测器的 ModelSim 仿真

6.5 任意序列检测器—感受 D 触发器的强大

6.5.1 完成饮料重量检测电路功能设计

6.5.2 优化检测电路的设计代码

第 7 章 时序逻辑电路的精华—计数器

7.1 简单的 16 进制计数器

7.1.1 两行代码完成计数器设计

7.1.2 计数器就是加法器和触发器

7.2 十进制计数器

7.2.1 带复位及时钟使能信号的计数器

7.2.2 讨论计数器的进制

7.2.3 计数器的花式写法

7.3 计数器才是流水灯的核心

7.3.1 设计一个秒信号

7.3.2 流水灯电路的设计方案

7.3.3 可控制闪烁频率的流水灯

7.3.4 采用移位运算设计流水灯电路

7.4 Verilog 的本质是并行语言

7.4.1 典型 Verilog 错误—同一信号重复赋值

7.4.2 并行语言与顺序语言

7.4.3 采用并行思维分析信号重复赋值问题

7.5 呼吸灯电路设计

7.5.1 呼吸灯的工作原理

7.5.2 设计思路分析

7.5.3 亮度实现模块 Verilog 设计

7.5.4 亮度控制模块 Verilog 设计

7.5.5 顶层模块 Verilog 设计

第三篇:入门篇

第 8 章 设计简洁美观的秒表电路

8.1.1 设定一个目标—4 位秒表电路功能

8.1.2 明确功能需求

8.1.3 形成设计方案

8.2 顶层文件的 Verilog 设计

8.3 设计一个完善的数码管显示模块

8.4 秒表计数模块的 Veilog 设计

8.4.1 一段式秒表计数电路设计

8.4.2 秒表计数电路的 ModelSim 仿真

8.4.3 简洁美观的秒表计时器设计

8.4.4 实现秒表的启停功能

8.5 按键消抖模块的 Verilog 设计

8.4.5 按键消抖产生的原理

8.4.6 消抖电路 Verilog 设计

8.4.7 按键消抖模块集成到秒表计数器中

第 9 章 数字密码锁电路设计

9.1 密码锁的功能描述

9.2 规划好密码锁的功能模块

9.2.1 密码锁总体结构框图

9.2.2 密码锁的顶层模块设计

9.3 密码锁功能子模块设计

9.3.1 按键消抖模块 Verilog 设计

9.3.2 计数模块 Verilog 设计

9.3.3 密码设置模块才是核心模块

第 10 章 简易电子琴电路设计

10.1 音符产生原理

10.2 琴键功能电路设计

10.2.1 顶层模块设计

10.2.2 琴键模块设计

10.2.3 音符产生模块设计

10.3 自动演奏乐曲“梁祝”

10.3.1 自动演奏乐曲原理

10.3.2 自动演奏乐曲“梁祝”片段

10.4 完整的电子琴电路设计

第 11 章 应用广泛的串口通信电路

11.1 RS-232 串口通信的概念

11.2 串口硬件电路原理分析

11.3 串口通信电路 Verilog 设计

11.3.1 顶层文件的 Verilog 设计

11.3.2 时钟模块的 Verilog 设计

11.3.3 接收模块的 Verilog 设计目 录

11.3.4 发送模块的 Verilog 设计

11.3.5 FPGA 实现及板载测试

11.4 采用串口控制秒表电路

11.4.1 设计需求分析

11.4.2 顶层文件的 Verilog 设计

11.4.3 时间获取模块 Verilog 设计

11.4.4 秒表电路顶层模块 Verilog 代码

11.4.5 计数器模块 Verilog 代码

11.3.6 FPGA 实现及板载测试

第 12 章 对状态机的讨论

12.1 有限状态机的概念

12.2 状态机的 Verilog 设计方法

12.2.1 一段式状态机 Verilog 代码

12.2.2 两段式状态机 Verilog 代码

12.2.3 三段式状态机 Verilog HDL 代码

12.3 计数器电路的状态机描述方法

12.4 序列检测器的状态机描述方法

第四篇:提高篇

第 13 章 基本的时序约束方法

13.1 电路的速度极限是什么

13.2 周期时序约束方法

13.2.1 查看计数器的逻辑电路结构

13.2.2 计数器电路添加时钟周期约束

13.3 速度与面积的取舍

13.3.1 多路加法器电路的结构分析

13.3.2 流水线操作的本质—多路加法器速度

13.3.3 用一个加法器完成 4 路加法

13.3.4 串行加法器时序分析

第 14 章 采用 IP 核设计

14.1 FPGA 设计中的拿来主义—使用 IP 核

14.1.1 IP 核的一般概念

14.1.2 FPGA 设计中的 IP 核类型

14.2 时钟 IP 核

14.2.1 全局时钟资源

14.2.2 采用时钟 IP 核生成多路时钟信号

14.3 乘法器 IP 核

14.4 存储器 IP 核

14.4.1 ROM 核

14.4.2 RAM 核

第 15 章 采用在线逻辑分析仪调试程序

15.1 在线逻辑分析仪的优势

15.2 GAO 的使用流程

15.3 采用 GAO 调试串口通信程序

15.3.1 调试目的

15.3.2 添加 GAO 到项目中

15.3.3 设置触发信号及触发条件

15.3.4 设置捕获信号参数

15.3.5 观察串口收发信号波形

第 16 章 常用 FPGA 设计技巧

16.1 默认管脚状态设置

16.2 复位信号的处理方法

16.3 合理利用时钟允许信号设计

16.4 利用移位相加实现乘法运算

16.5 根据芯片结构制定设计方案

16.6 浮点乘法器设计

16.6.1 单精度浮点数据格式

16.6.2 单精度浮点数乘法运算分析

16.6.3 自定义浮点数格式

16.6.4 自定义浮点数乘法算法设计

16.6.5 算法 Verilog 实现

祝大家学习愉快,工作顺利。