时间:2025-02-26 来源:FPGA_UCY 关于我们 0

文章目录

一、HLS简介

HLS(High-Level )高层综合,就是将 C/C++的功能用 RTL 来实现,将 FPGA 的组件在一个软件环境中来开发,这个模块的功能验证在软件环境中来实现,无缝的将硬件仿真环境集合在一起,使用软件为中心的工具、报告以及优化设计,很容易的在 FPGA 传统的设计工具中生成 IP。

传统的 FPGA 开发,首先写 HDL 代码,然后做行为仿真,最后做综合、时序分析等,最后生成可执行文件下载到 FPGA 使用,开发周期比较漫长。

使用 HLS,用高级语言开发可以提高效率。

因为在软件中调试比硬件快很多,在软件中可以很容易的实现指定的功能,而且做 RTL仿真比软件需要的时间多上千倍。

二、安装

可参考以下网址,包含了下载及安装破解

三、HLS实现流水灯开发实例 3.1 创建HLS工程

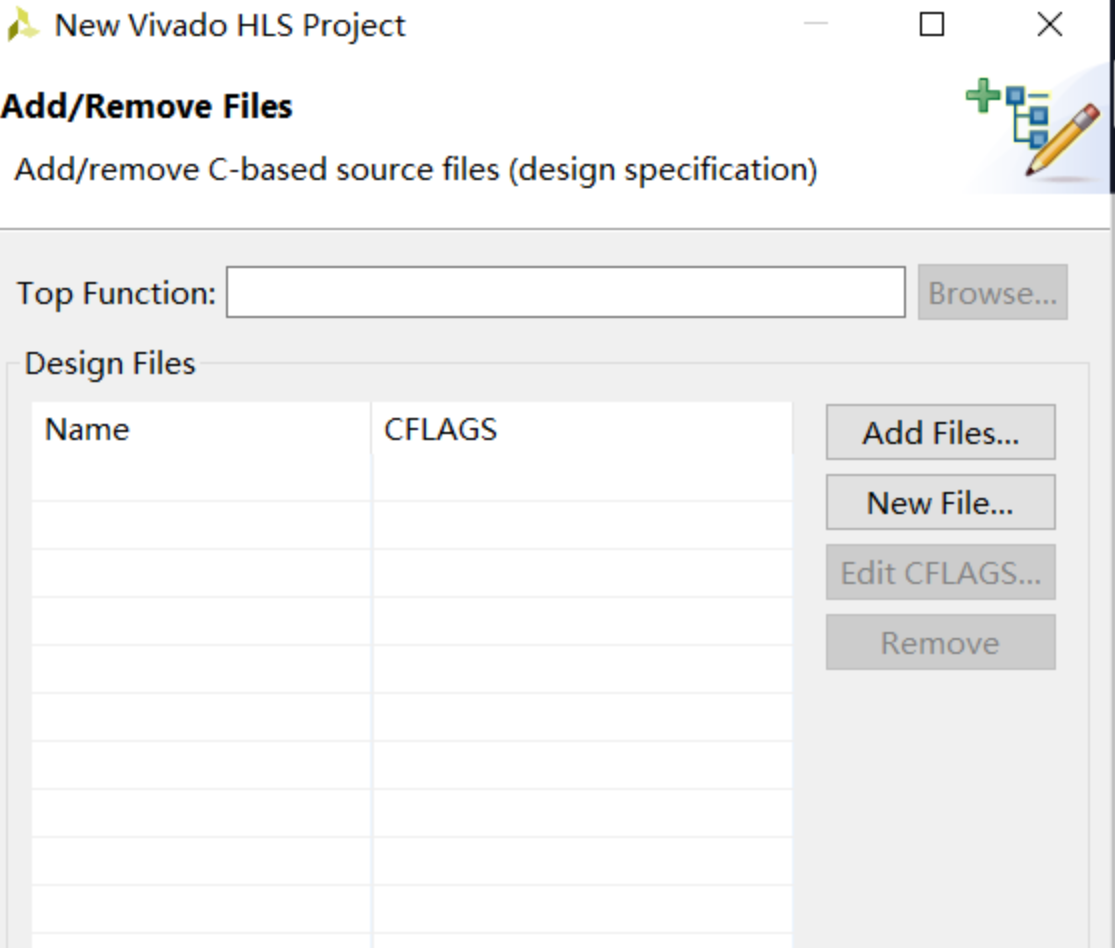

选择顶层函数,此处暂不管

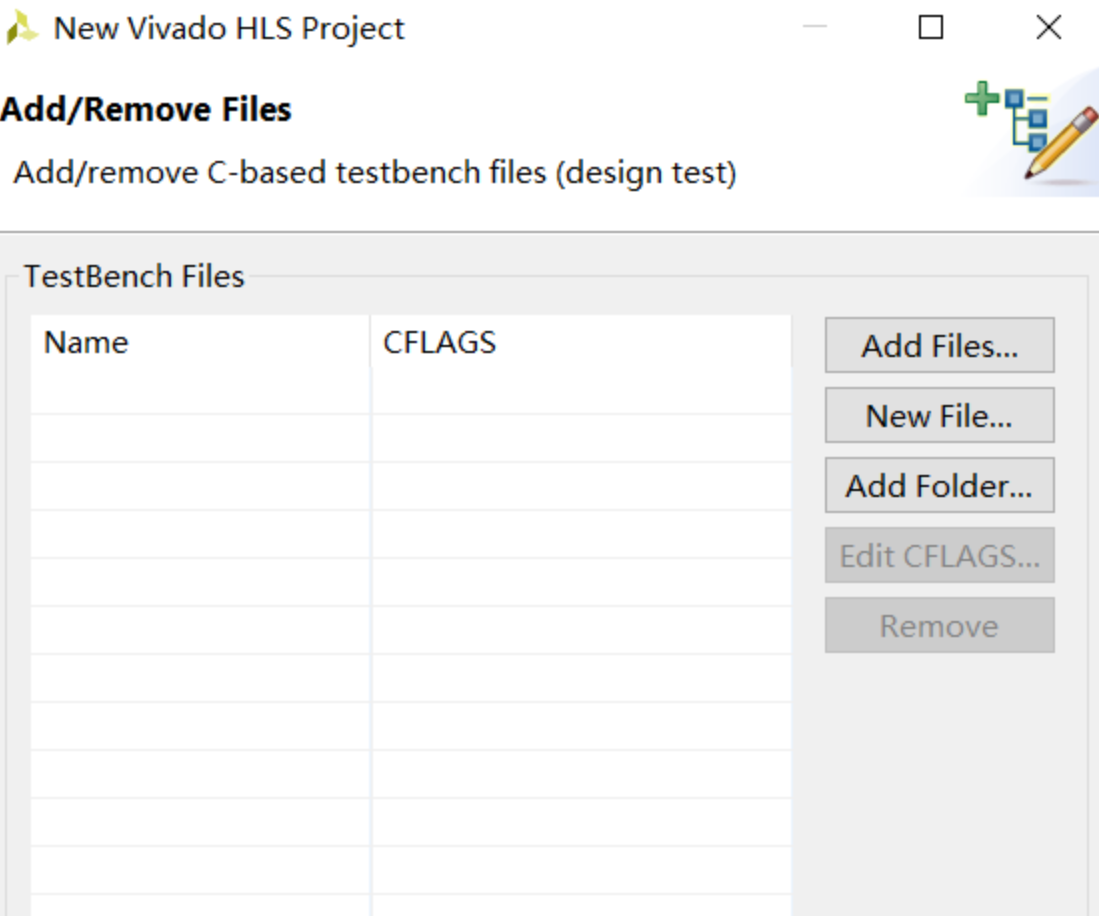

选择添加C仿真文件,此处暂不管

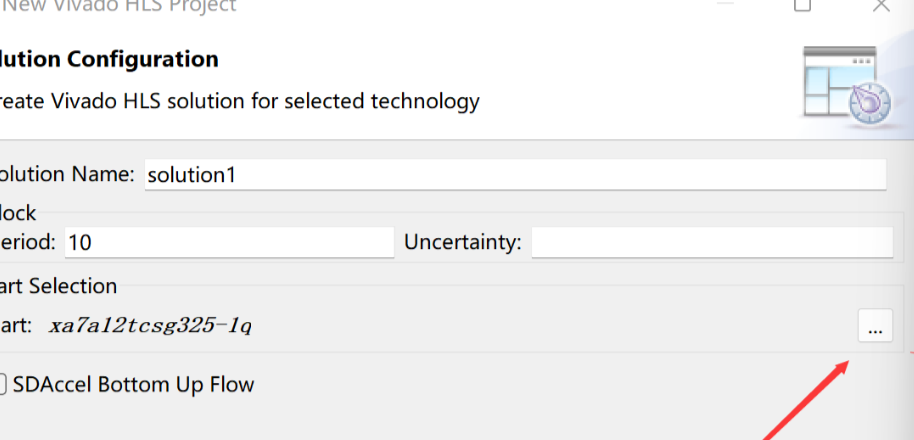

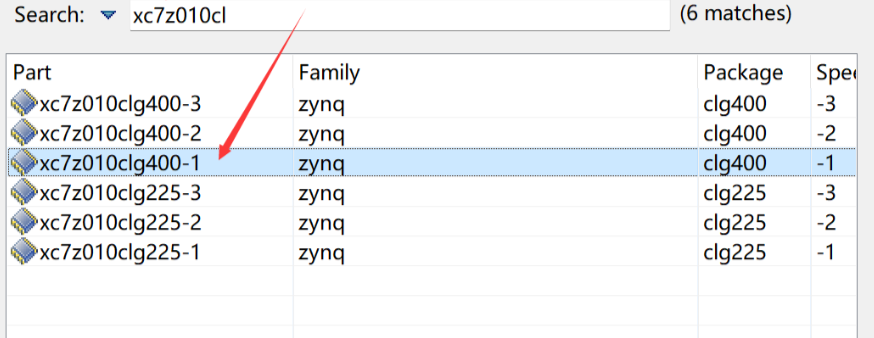

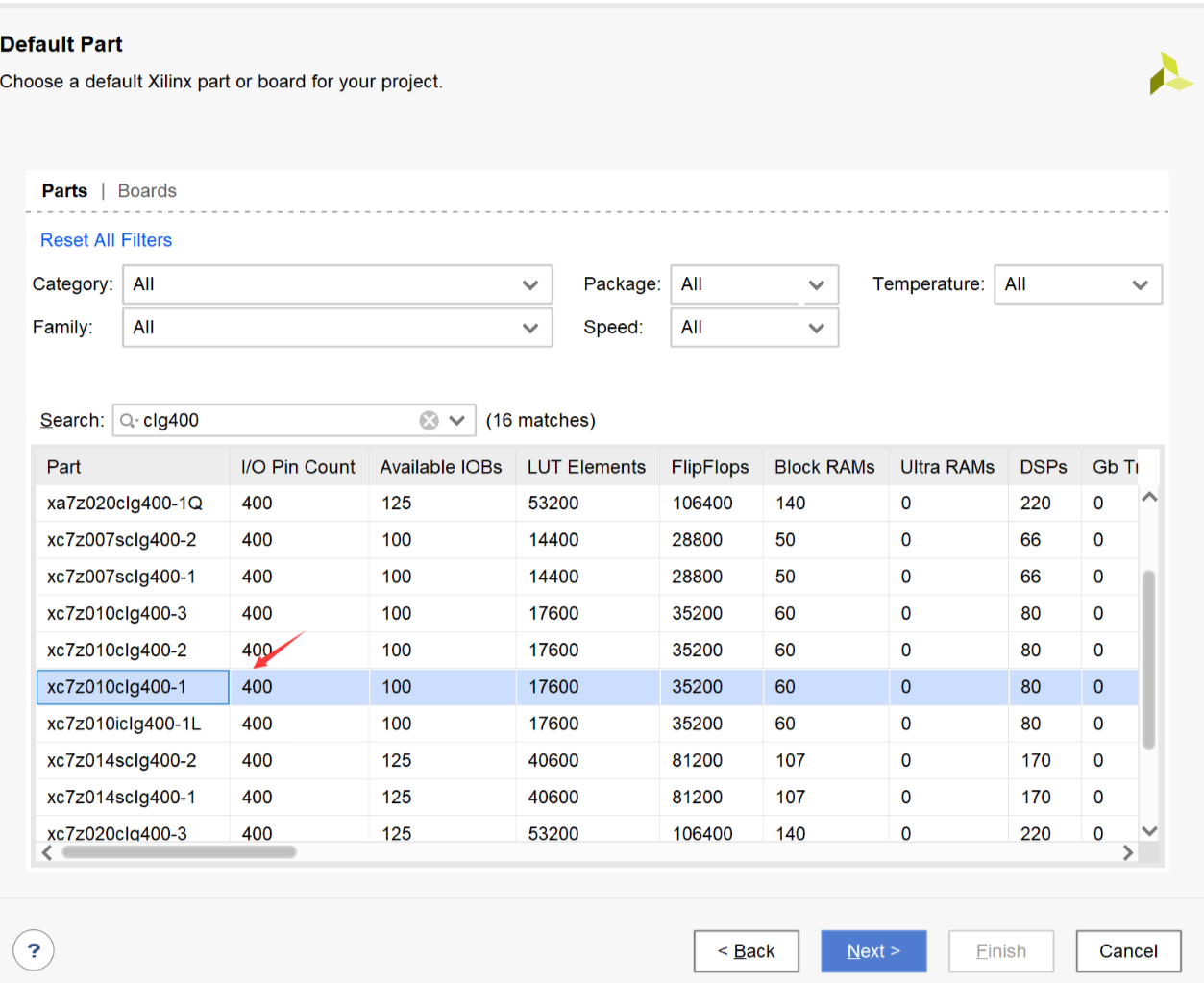

选择相应器件

3.2 代码编写

添加文件

①源文件添加

点击,右键后,选择New File,创建文件

具体代码如下:

led.h

#ifndef _SHIFT_LED_H_

#define _SHIFT_LED_H_

#include "ap_int.h"

#define CNT_MAX 100000000

//#define CNT_MAX 100,100M时钟频率下计数一秒钟所需要的计数次数

#define FLASH_FLAG CNT_MAX-2

// typedef int led_t;

// typedef int cnt_t;

typedef ap_int<1> led_t;

typedef ap_int<32> cnt_t;

void flash_led(led_t *led_o , led_t led_i);

#endif

led.cpp

#include "led.h"

void flash_led(led_t *led_o , led_t led_i){

#pragma HLS INTERFACE ap_vld port=led_i

#pragma HLS INTERFACE ap_ovld port=led_o

cnt_t i;

for(i=0;i<CNT_MAX;i++){

if(i==FLASH_FLAG){

*led_o = ~led_i;

}

}

}

②仿真测试文件添加

右键Test Bench,选择New File

具体代码如下:

.cpp

#include "led.h"

#include 3.3 综合仿真

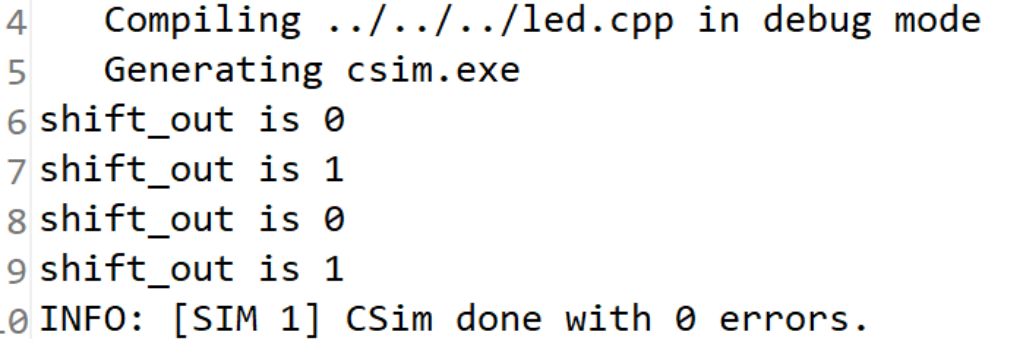

点击->Run C (输出01交替,表示C仿真结果正确)

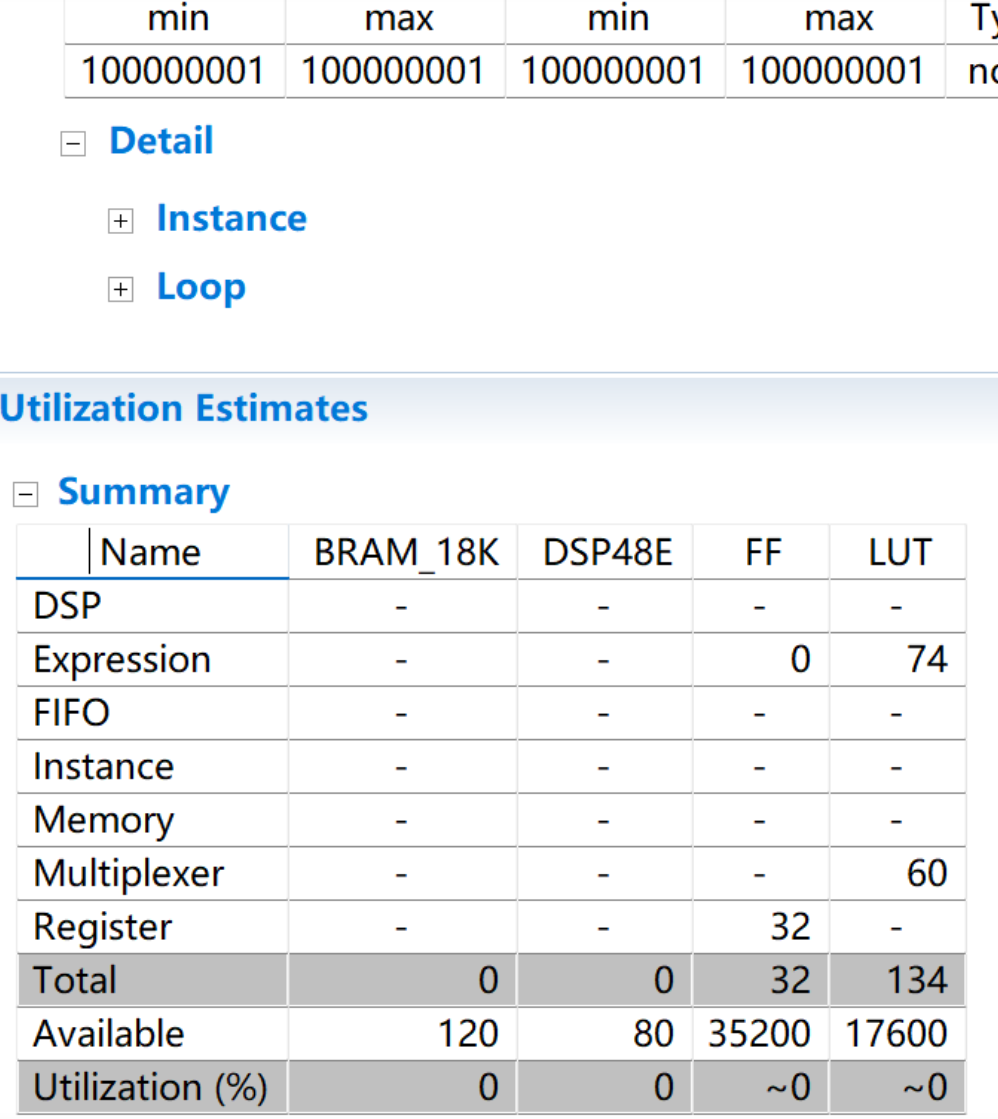

点击->Run C ->

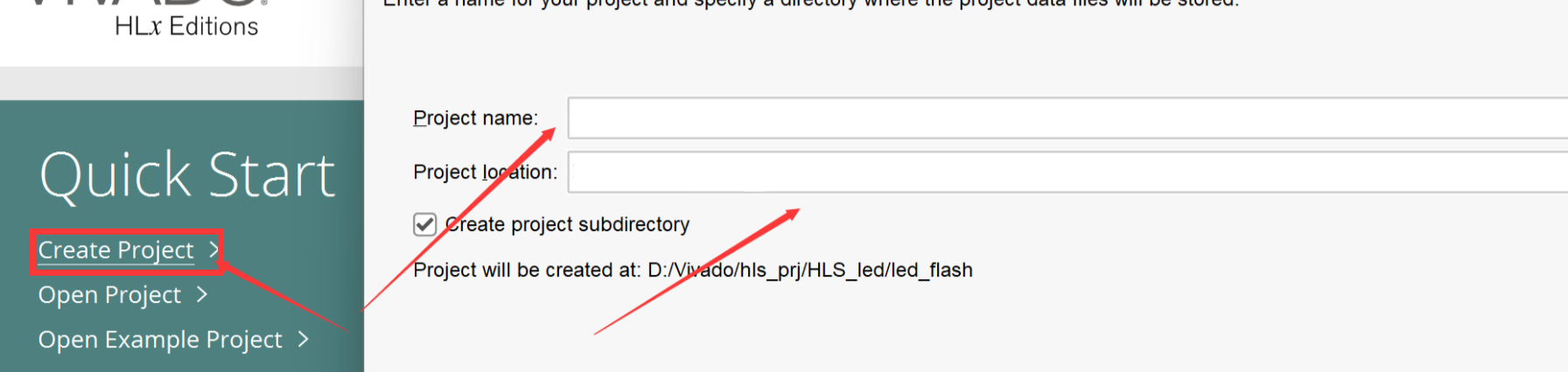

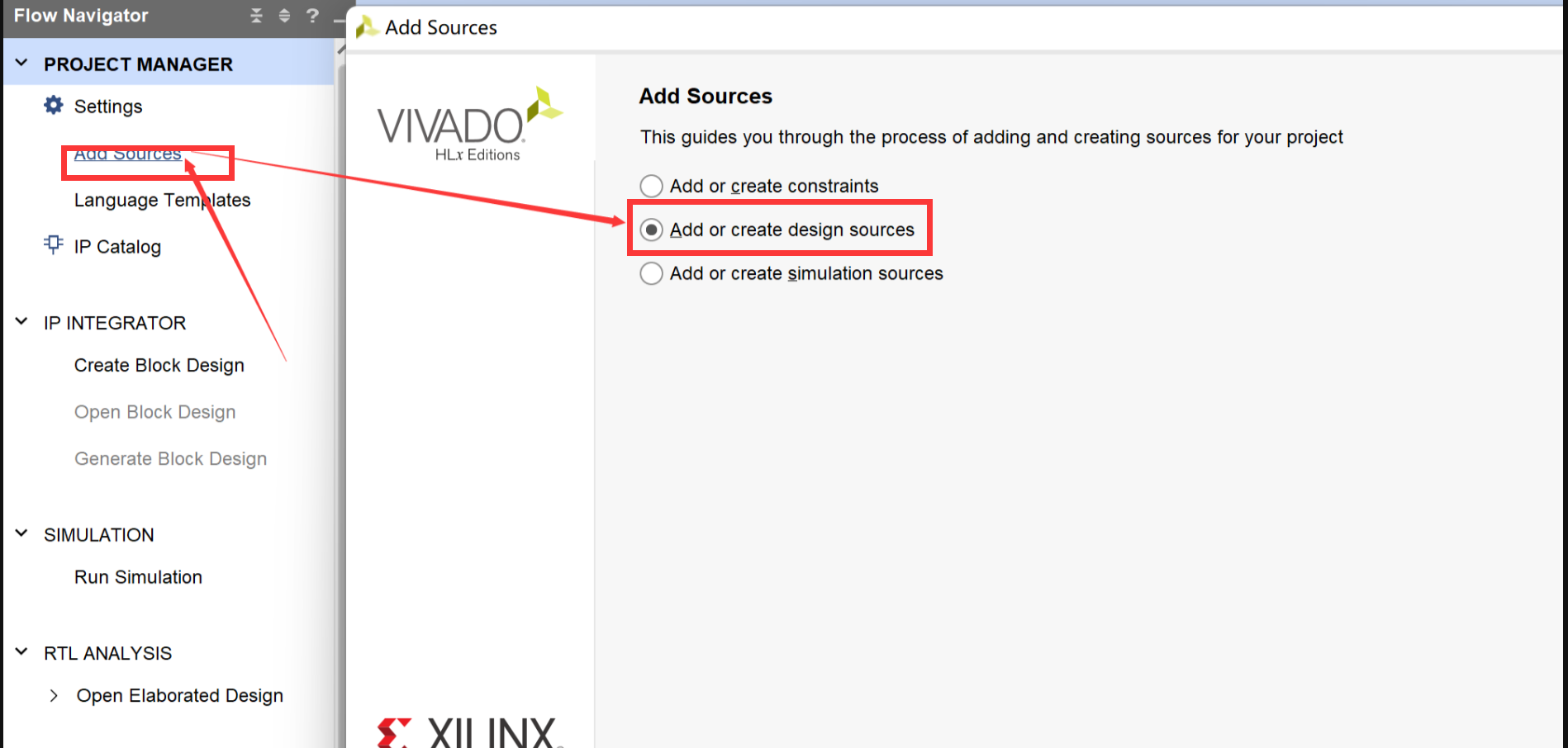

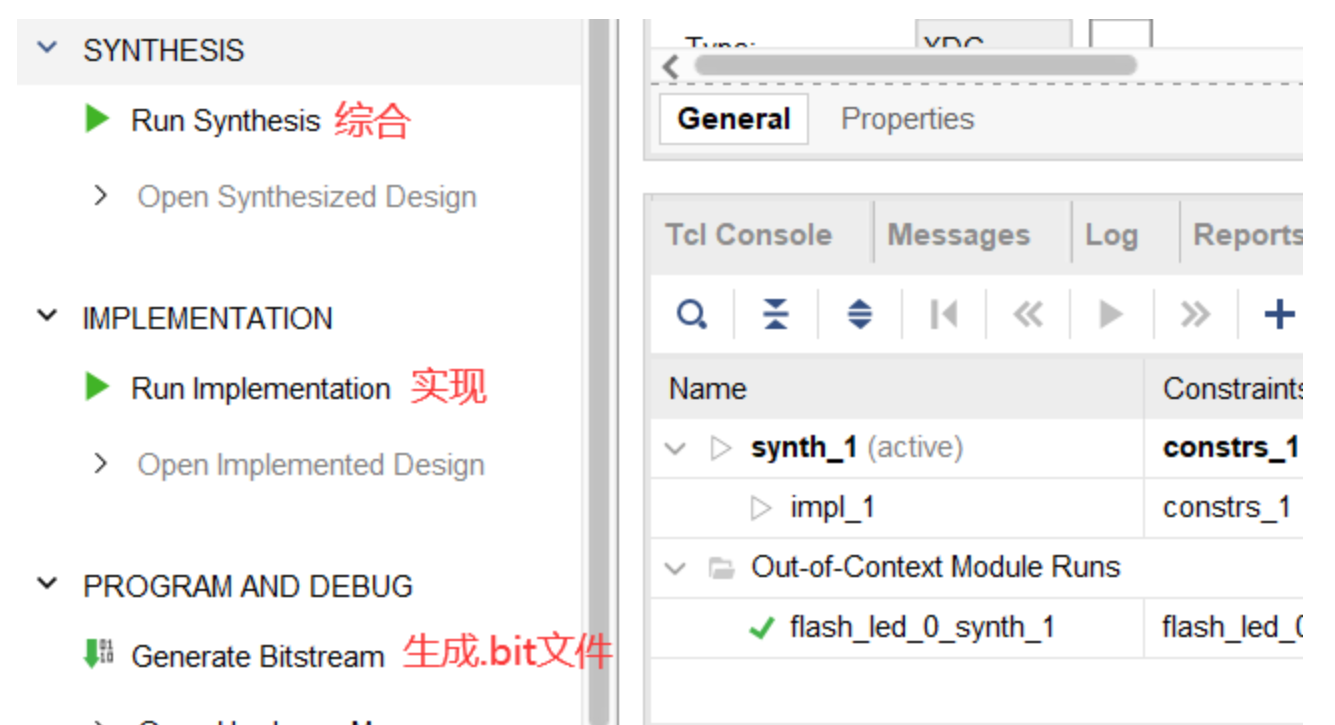

3.4 创建工程

按照下列图片实例进行即可:

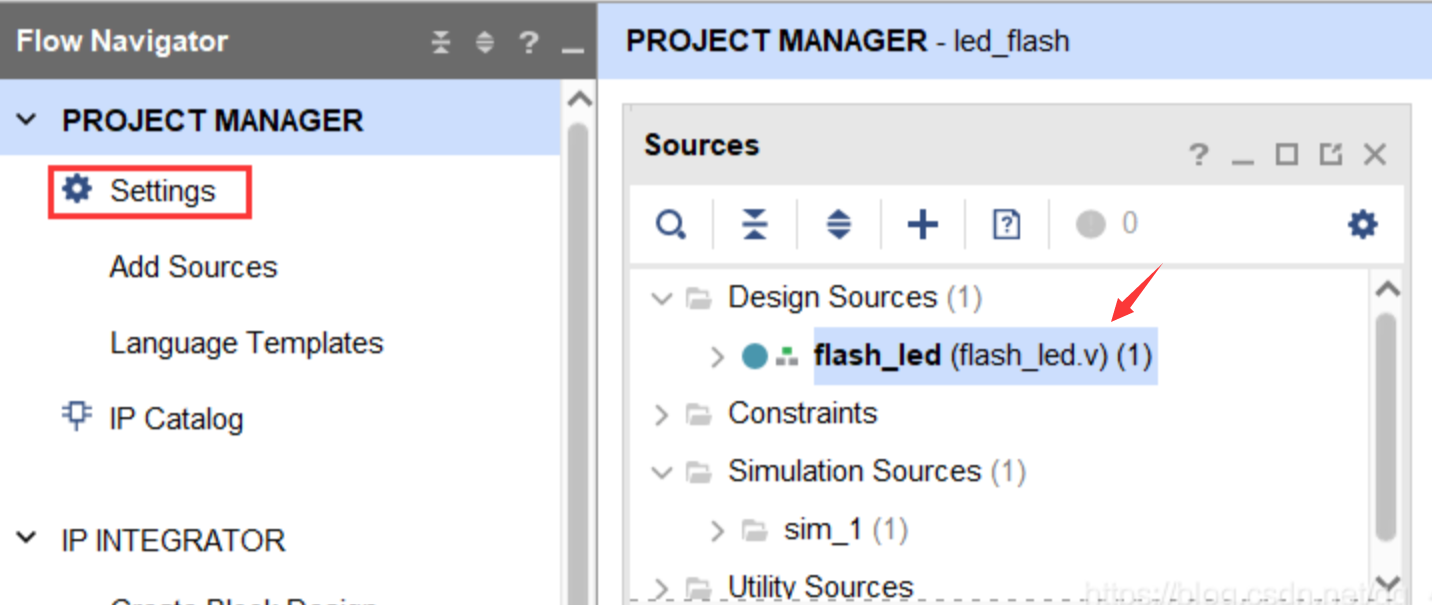

选择IP->,并且点击加号,选择,将会自动识别到IP,识别到后,点击Apply->OK

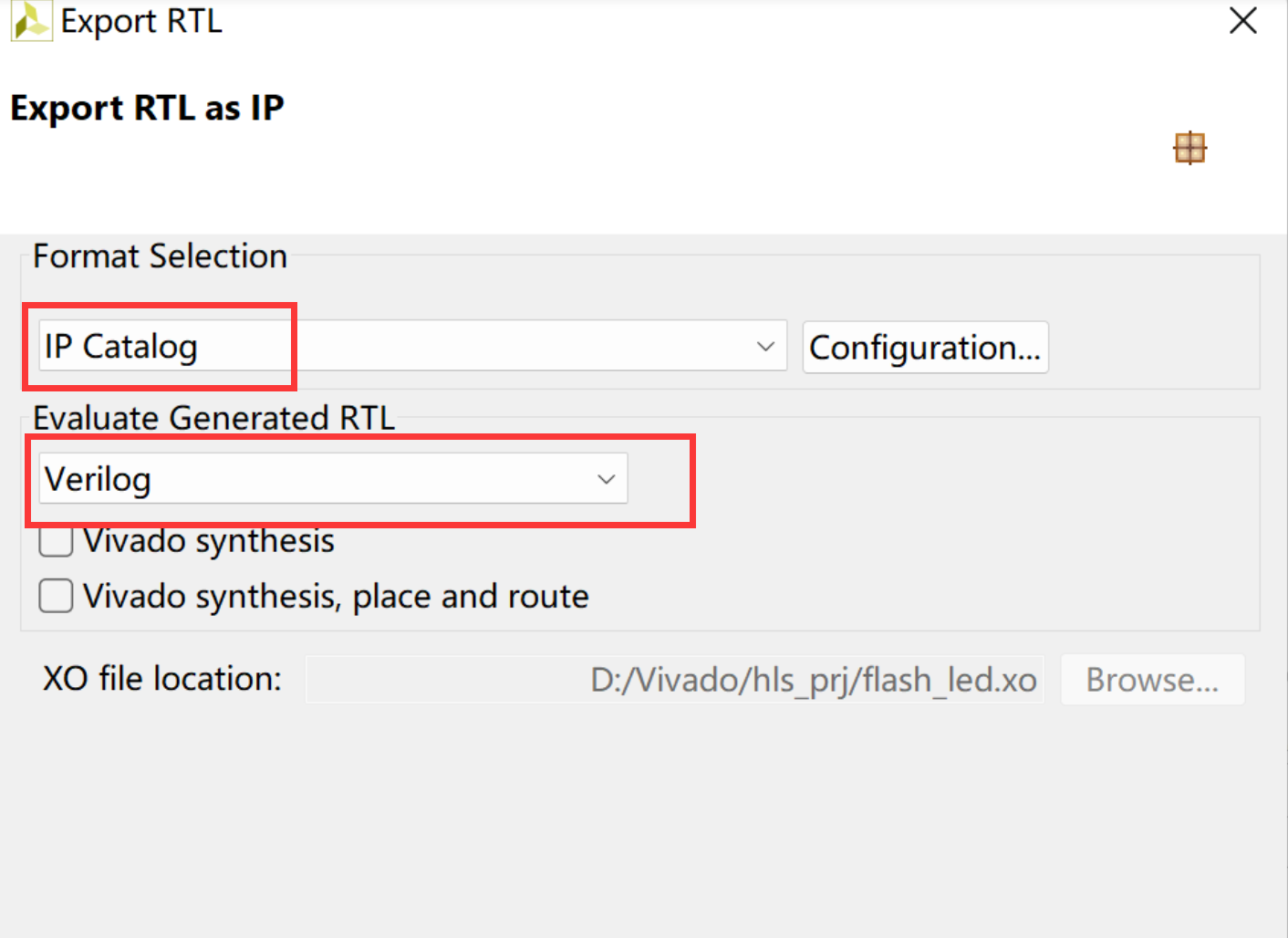

生成IP:

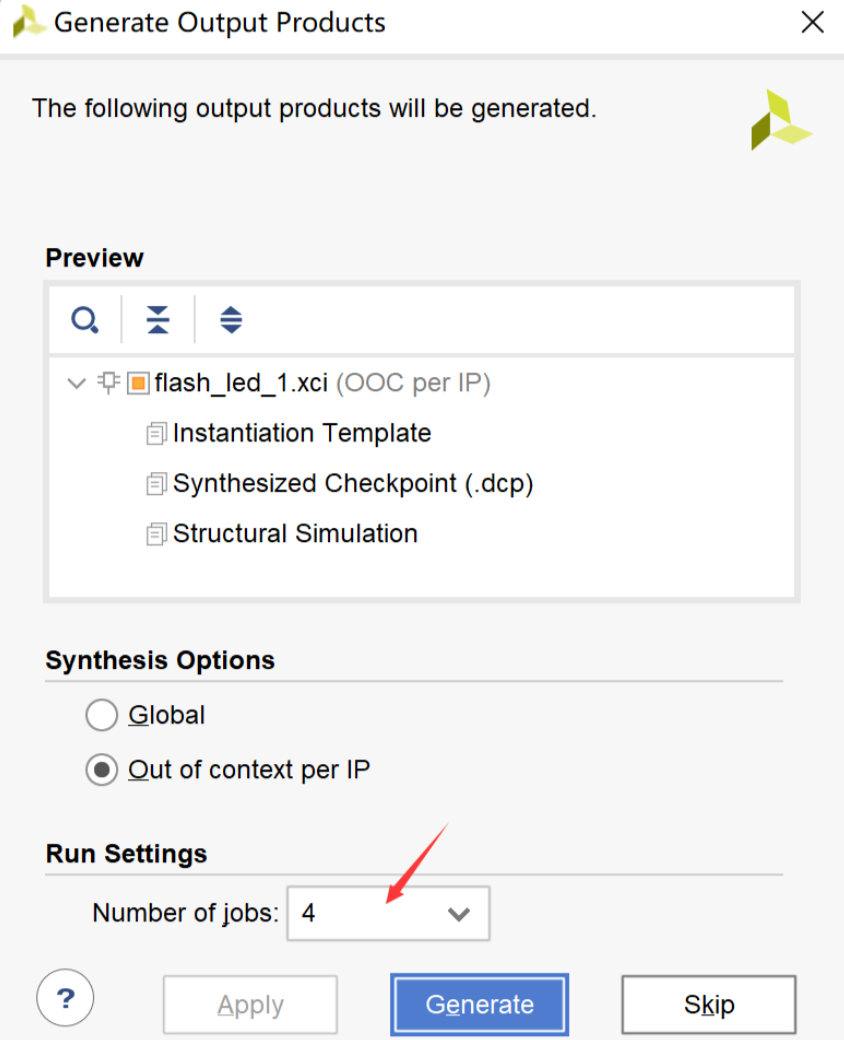

双击,默认选择

创建源文件,具体代码如下:

`timescale 1ns / 1ps

module flash_led(

input wire clk ,

input wire rst_n ,

output wire led_o

);

wire rst ;//同步复位

wire ap_ready ;//当前可以接收下一次数据

reg ap_start ;//IP 开始工作

reg led_i_vld ;//输入数据有效

wire led_o_vld ;

reg led_i ;//输入的 led 信号

wire led_o_r ;

wire ap_done ;

wire ap_idle ;

reg [1:0] delay_cnt ;

assign rst = ~rst_n ;

assign led_o = led_o_r ;

//----------------delay_cnt------------------

always @(posedge clk) begin

if (rst==1'b1) begin

delay_cnt <= 'd0;

end

else if(delay_cnt[1]==1'b0) begin

delay_cnt <= delay_cnt + 1'b1;

end

end

//----------------ap_start------------------

always @(posedge clk) begin

if (rst==1'b1) begin

ap_start <= 1'b0;

end

else if(delay_cnt[1]==1'b1)begin

ap_start <= 1'b1;

end

end

//----------------led_i_vld------------------

always @(posedge clk) begin

if (rst==1'b1) begin

led_i_vld <= 1'b0;

end

else if(delay_cnt[1]==1'b1)begin

led_i_vld <= 1'b1;

end

end

//----------------ap_i------------------

always @(posedge clk) begin

if (rst==1'b1) begin

led_i <= 1'b0;

end

else if(led_o_vld==1'b1)begin

led_i <= led_o_r ;

end

end

flash_led_0 inst_flash_led (

.led_o_V_ap_vld(led_o_vld), // output wire led_o_V_ap_vld

.led_i_V_ap_vld(led_i_vld), // input wire led_i_V_ap_vld

.ap_clk(clk), // input wire ap_clk

.ap_rst(rst), // input wire ap_rst

.ap_start(ap_start), // input wire ap_start

.ap_done(ap_done), // output wire ap_done

.ap_idle(ap_idle), // output wire ap_idle

.ap_ready(ap_ready), // output wire ap_ready

.led_o_V(led_o_r), // output wire [0 : 0] led_o_V

.led_i_V(led_i) // input wire [0 : 0] led_i_V

);

endmodule

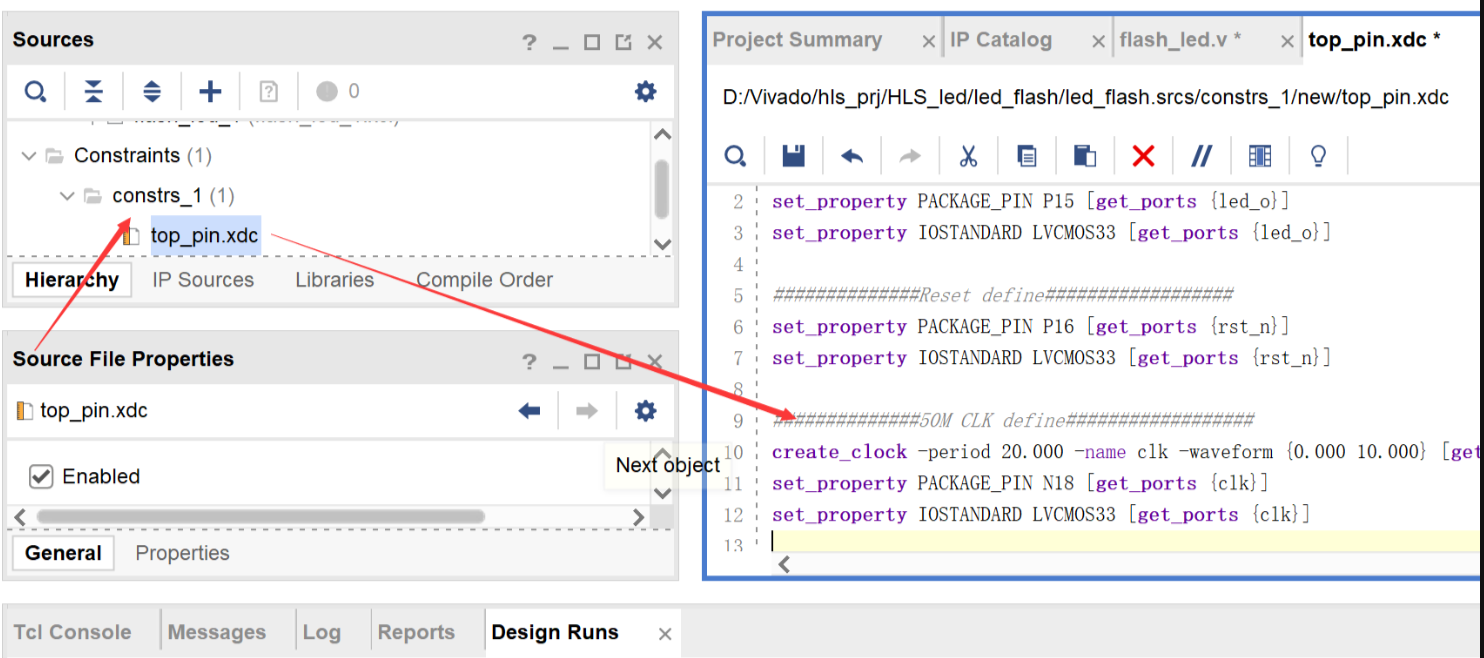

具体代码如下:

##############LED define##################

set_property PACKAGE_PIN P15 [get_ports {led_o}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_o}]

##############Reset define##################

set_property PACKAGE_PIN P16 [get_ports {rst_n}]

set_property IOSTANDARD LVCMOS33 [get_ports {rst_n}]

##############50M CLK define##################

create_clock -period 20.000 -name clk -waveform {0.000 10.000} [get_ports clk]

set_property PACKAGE_PIN N18 [get_ports {clk}]

set_property IOSTANDARD LVCMOS33 [get_ports {clk}]

运行结果如下:

四、总结

本次实验了解了什么是HLS,让我明白了在硬件逻辑难以实现的情况下,我们也可以通过利用C这样的高级语言程序编写逻辑,交由编辑器进行转换,虽然会耗费更多的资源,但可以为开发者节省下宝贵的时间

五、参考资料