时间:2025-02-07 来源:FPGA_UCY 关于我们 0

序言

文章内容均为本人在学习FPGA时所了解到的知识,若有不足与错误,还请指教,本人不胜感激。另这只是第一部分有关FPGA的基础知识,后面还会继续更新本人的学习历程,包括在学习过程中所接触的一些项目和代码以及在学习过程中可能出现的问题和问题的解决办法等。

目录

一、FPGA是什么?

FPGA 是一种硬件可重构的体系结构。它的英文全称是Field Gate Array,中文名是现场可编程门阵列。其本身为集成电路的一种,其发展也体现在集成电路的发展中;FPGA本身的优势有很多,特别是跟CPU、GPU和专用ASIC相比,有其本身的特点;结合这些优势,FPGA在很多领域无法被替代。

FPGA(Field Gate Array)是在PAL (可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA本质也是一种芯片,是一种以数字电路为主的集成芯片。

FPGA于 1985 年由 创始人之一 Ross 发明,属于可编程逻辑器件( Logic ,PLD)的一种。这个时间比著名的摩尔定律出现的时间晚 20 年左右,但是 FPGA 一经发明,后续的发展速度之快,超出大多数人的想象。

二、初识FPGA。 (一)FPGA工作原理

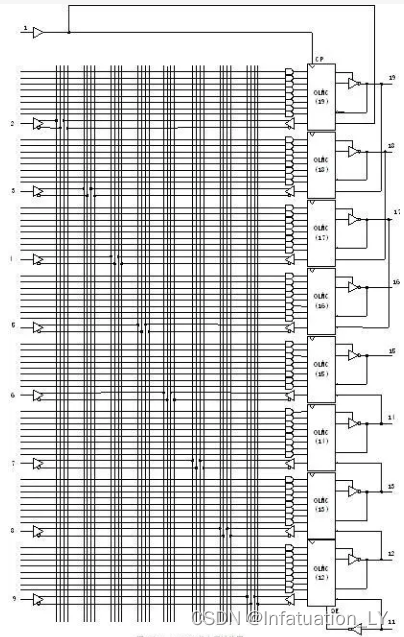

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB( Logic Block)、输入输出模块IOB(Input Block)和内部连线()三个部分。 现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构。FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

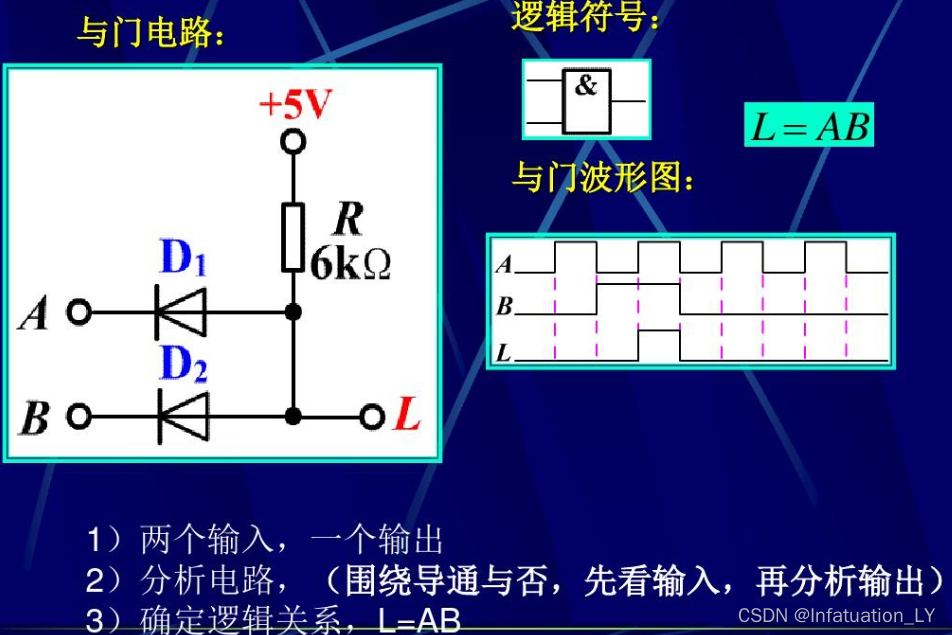

(二)基本门电路 (1)与门(AND gate)

与门又称“与电路”、逻辑“积”、逻辑“与”电路。是执行“与”运算的基本逻辑门电路。与门有多个输入端,一个输出端。当所有的输入同时为高电平(逻辑1)时,输出才为高电平,否则输出为低电平(逻辑0)。

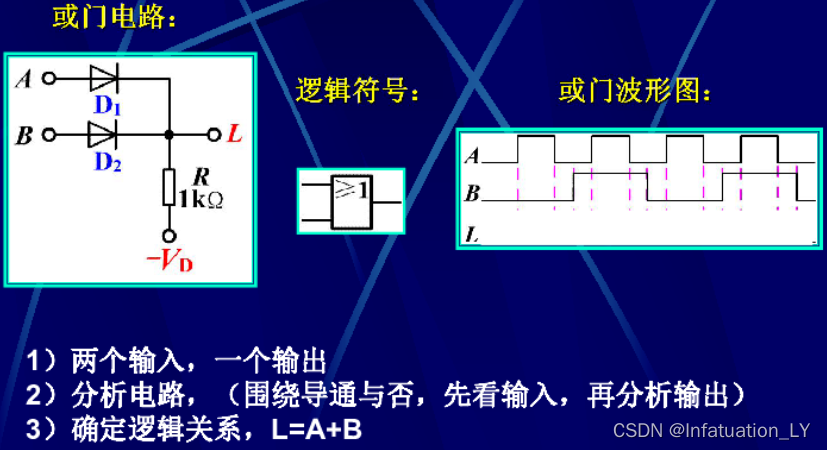

(2)或门(OR gate)

或门又称或电路、逻辑和电路。如果几个条件中,只要有一个条件得到满足,某事件就会发生,这种关系叫做“或”逻辑关系。具有“或”逻辑关系的电路叫做或门。或门有多个输入端,一个输出端,只要输入中有一个为高电平时(逻辑“1”),输出就为高电平(逻辑“1”);只有当所有的输入全为低电平(逻辑“0”)时,输出才为低电平(逻辑“0”)。

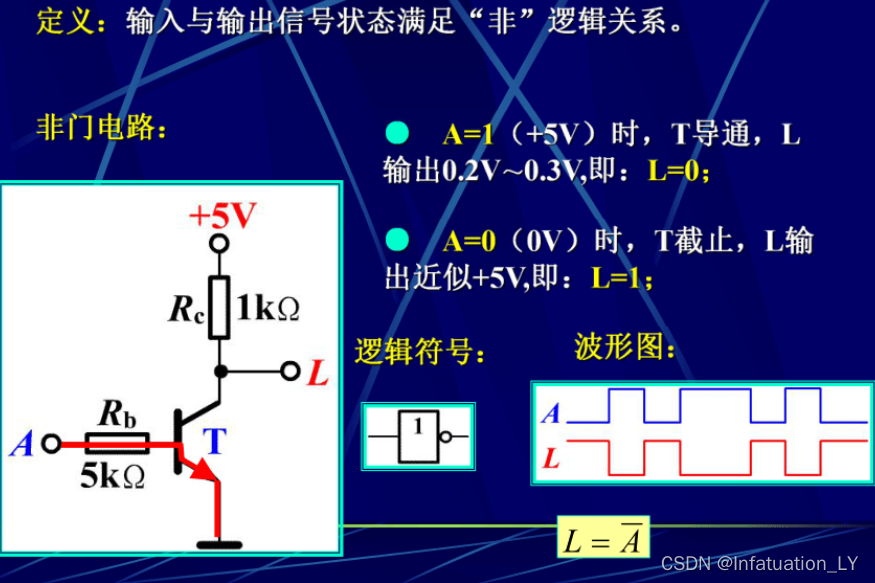

(3)非门(NOT gate)

非门又称非电路、反相器、倒相器、逻辑否定电路,简称非门,是逻辑电路的基本单元。非门有一个输入和一个输出端。当其输入端为高电平(逻辑1)时输出端为低电平(逻辑0),当其输入端为低电平时输出端为高电平。输入端和输出端的电平状态总是反相的。非门的逻辑功能相当于逻辑代数中的非,电路功能相当于反相,这种运算也称非运算。

(三)FPGA发展历程

PAL→GAL→CPLD→FPAG

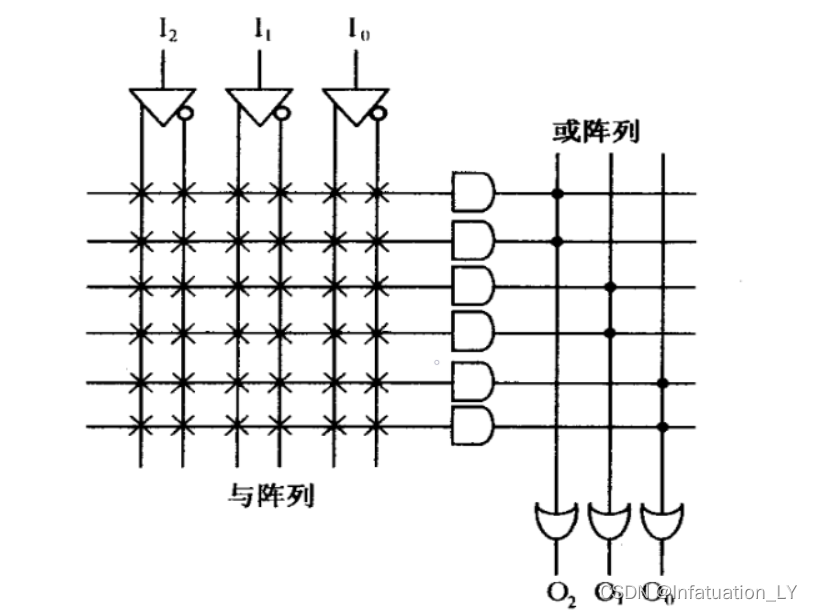

(1)PAL (可编程阵列逻辑)

由可编程的与阵列、固定的或阵列和输出反馈单元组成的一种可编程逻辑器件。输出和反馈结构由可编程的与阵列和固定的或阵列组成,没有输出反馈信号,输入和输出引出端是固定的,不能由用户自行定义。只适用于简单的组合逻辑电路设计。

(2)GAL(通用阵列逻辑)

GAL是在PAL的基础上设计出来的器件,即通用阵列逻辑器件。GAL首次在PLD上采用了工艺,使得其具有电可擦除重复编程的特点,彻底解决了熔丝型可编程器件的一次可编程问题。

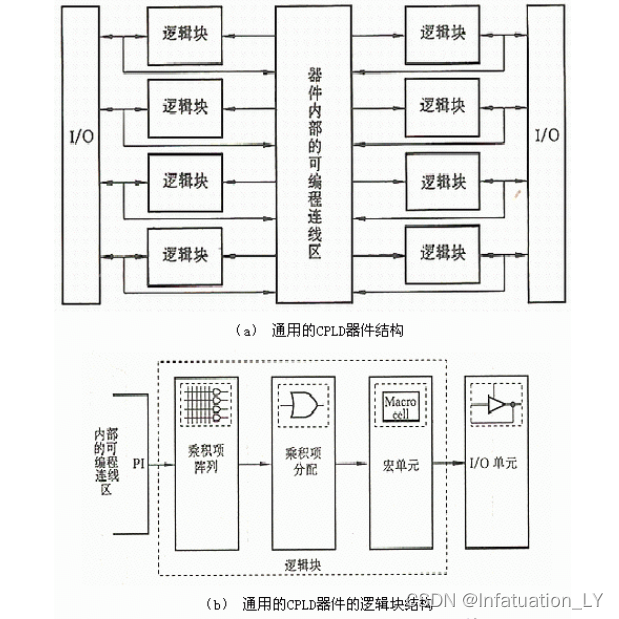

(3)CPLD(复杂可编程逻辑器件)

CPLD采用CMOS EPROM、、快闪存储器和SRAM等编程技术,从而构成了高密度、高速度和低功耗的可编程逻辑器件。

(四)芯片的分类 (1)定制电路

内部电路固定,例如:CPU、GPU等。

(2)半定制电路

内部电路可更改,例如:FPGA等。

(五)FPGA的优势

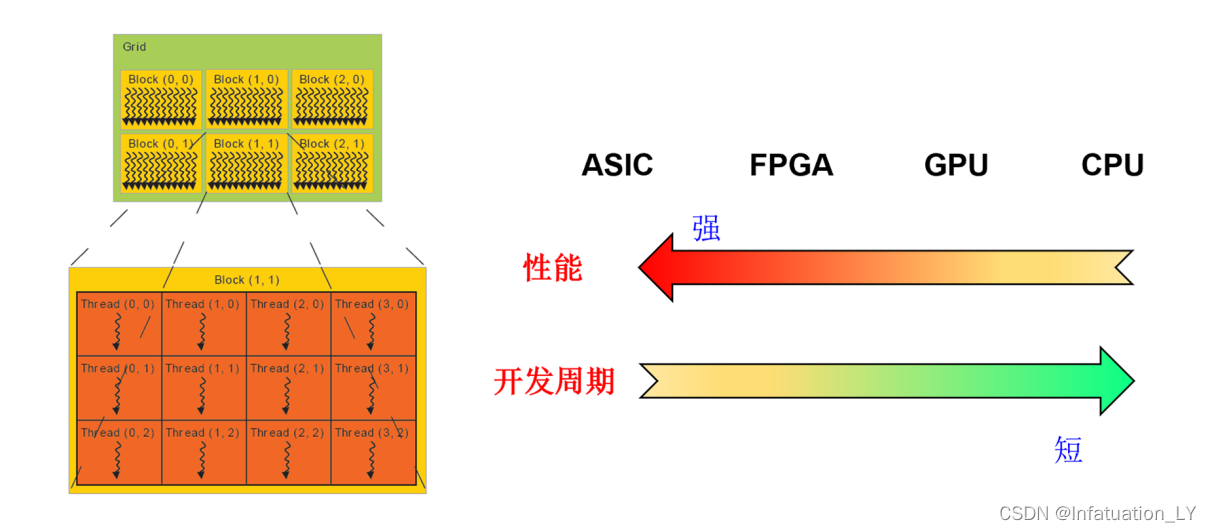

与CPU、GPU、ASIC相比,FPGA主要存在如下四个方面的优势:并行处理、延迟小、逻辑可实时改变和开发周期短。

(1)并行处理

FPGA的代码(固件)最终会转换成实际的电路,因此所有的信号处理都是并行完成的。如图所示为以图像识别为例,说明四种芯片的特点。在性能方面FPGA的性能仅仅次于ASIC,但是在开发周期方面FPGA的开发周期又小于ASIC的开发周期。所以在商业应用中,FPGA可以在较短时间(先于ASIC)实现性能相当优越(优于CPU和GPU)的系统迅速占领市场。

各种处理芯片优缺点对比

(2)延迟小

ASIC和FPGA一样,所有模块同时工作,延时以时钟周期位为单位,延时比较小。而CPU/GPU执行一条语句需要多个周期,一个任务需要多条语句。

(3)逻辑可实时改变

由于FPGA是基于RAM的查找表技术实现的,而RAM值可实时擦写,所以由FPGA实现的功能可以实时的改变。

(4)开发周期短

FPGA相对ASIC而言,开发周期短,可迅速占领市场。

(5)FPGA的应用领域

从使用的角度看(不考虑应用领域),FPGA可以应用在如下五个方面:自动控制、通信、数据获取、数据处理和抗辐照电子学。

在自动控制领域,FPGA可以实现高精度的自控系统已经专用探测系统。虽然MCU可以实现一定的控制功能,但是仅限于慢速控制,对于高频信号、高频时钟等要求高精度高速控制的领域,FPGA能发挥无可替代的作用。

在通信领域,FPGA可以应用在各种通信中,包括各种片上总线、系统总线、现场总线、并行通信、串行通信、无线通信等等。例如:PCI、PCIe、RS485、I2C、VME、光纤、蓝牙、、CAN。

在数据获取领域,FPGA主要用于数据读取、预处理、传输、存储等。例如引用在高能粒子探测器系统中。

在数据处理领域,FPGA可以应用于各种算法的加速,包括图像、视频、语音处理及AI算法等。例如:人脸识别、车牌识别和语音识别等。

在抗辐照电子学领域,除了设计专用ASIC外,FPGA可以实现抗辐照功能,引用在卫星、火星车等项目中。

(六)硬件描述语言

硬件描述语言→编写内部电路→实现相应的功能

(1)什么是硬件描述语言

硬件描述语言( , HDL)是电子系统硬件行为描述、结构描述、数据流描述的语言。利用这种语言,数字电路系统的设计可以从顶层到底层(从抽象到具体)逐层描述自己的设计思想,用一系列分层次的模块来表示极其复杂的数字系统。然后,利用电子设计自动化( , EDA )工具,逐层进行仿真验证,再把其中需要变为实际电路的模块组合,经过自动综合工具转换到门级电路网表。接下去,再用专用集成电路( ,ASIC)或现场可编程门阵列 FPGA(Field- Gate Array,FPGA)自动布局布线工具,把网表转换为要实现的具体电路布线结构,VHDL(Very High Speed ,HDL)和 HDL 语言适应了这种趋势的要求,先后成为 IEEE 标准。

(2)主要的硬件描述语言

硬件描述语言主要包括:、VHDL、。

HDL拥有广泛的设计群体,成熟的资源也比 VHDL 丰富,语言从C编程语言中继承了多种操作符和结构,对于熟悉C语言的同学,学习时上手会很快。

VHDL超高速集成电路硬件描述语言(Very High Speed ,VHDL)是一种标准化程度较高的硬件描述语言,其语言特点包括:语法严谨、结构规范、移植性强、数据类型丰富。除此之外VHDL支持层次结构设计,独立于器件和设计平台,程序复用性强。

结合了来自 、VHDL、C++的概念,将硬件描述语言与现代的高层级验证语言结合了起来。所以有上述两种语言和计算机高级语言的特征。

在中国很多集成电路设计公司都采用,一般大型项目采用VHDL。是的升级,对于“小白”,应该从学习开始。

(七)与VHDL

HDL和VHDL都是用于逻辑设计的硬件描述语言,并且都已成为IEEE标准。

VHDL是在1987年成为IEEE标准, HDL则在1995年才正式成为IEEE标准。之所以VHDL比 HDL早成为IEEE标准,这是因为VHDL是美国军方组织开发的,而 HDL 则是从一个普通的民间公司的私有财产转化而来,基于 HDL的优越性,才成为的IEEE标准,因而有更强的生命力。

VHDL 其英文全名为VHSIC ,而VHSIC则是Very High Speed 的缩写词,意为甚高速集成电路,故VHDL其准确的中文译名为甚高速集成电路的硬件描述语言。

HDL和VHDL作为描述硬件电路设计的语言,其共同的特点在于:能形式化地抽象表示电路的结构和行为、支持逻辑设计中层次与领域的描述、可借用高级语言的精巧结构来简化电路的描述、具有电路仿真与验证机制以保证设计的正确性、支持电路描述由高层到低层的综合转换、硬件描述与实现工艺无关(有关工艺参数可通过语言提供的属性包括进去)、便于文档管理、易于理解和设计重用。

但是 HDL和VHDL又各有其自己的特点。

由于 HDL早在1983年就已推出,至今已有十三年的应用历史,因而 HDL拥有更广泛的设计群体,成熟的资源也远比VHDL丰富。

与VHDL相比的最大优点是:它是一种非常容易掌握的硬件描述语言,只要有C语言的编程基础,通过二十学时的学习,再加上一段实际操作,一般同学可在二至三个月内掌握这种设计技术。

而掌握VHDL设计技术就比较困难。这是因为VHDL不很直观,需要有Ada编程基础,一般认为至少需要半年以上的专业培训,才能掌握VHDL的基本设计技术。

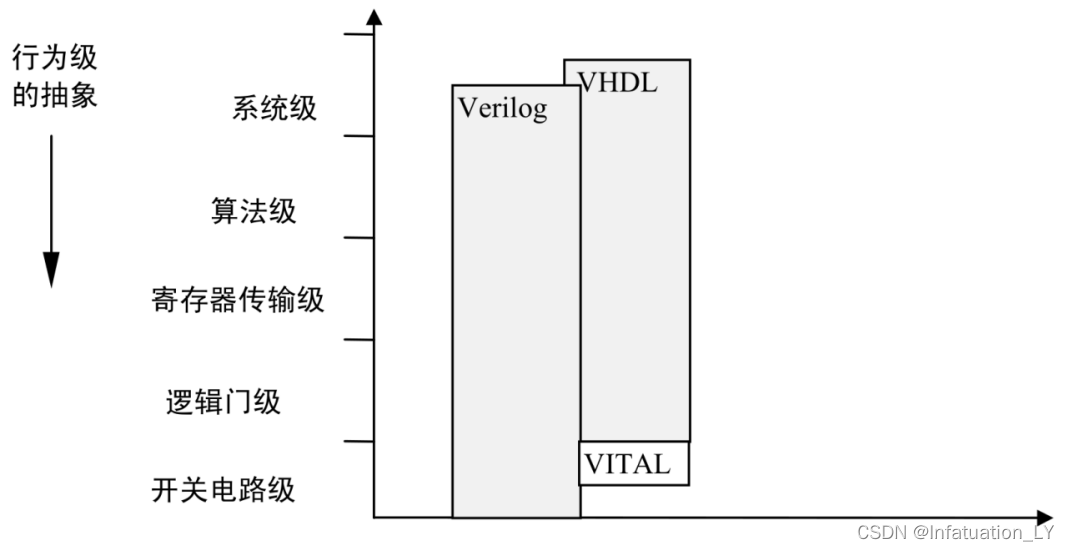

目前版本的 HDL和VHDL在行为级抽象建模的覆盖范围方面也有所不同。一般认为 HDL在系统级抽象方面比VHDL略差一些,而在门级开关电路描述方面比VHDL强得多。

三、FPGA设计流程。

1.需求分析

2.模块划分

3.代码编写

4.综合前仿真(功能仿真)

5.综合(管脚约束)

6.布局布线(各个门级电路添加延时)

7.综合后仿真(时序仿真)

8.生成bit流

9.上板验证

四、的使用。 五、语法。 (一)数据类型

常量:(全局参数)、(本地参数)(详细解释:与)

变量:reg(寄存器类型)、wire(线网型)(详细解释:reg与wire)

注:定义变量时要注意位宽(后面会讲)。

(二)运算符与表达式

算数运算符:+、-、*、/、%(取模)

条件运算符(三目运算符): d = (a==1) ? 1:0;

位运算符:&(按位于)、|(按位或)、~(位取反)、^(按位异或)、^~(按位同或)

关系运算符:、=、==、!=、===(严格等于)、!==(严格不等于)

逻辑运算符:&&、 ||、!(结果只有0或1)

位拼接运算符:{}(将两个或者多个信号的某些位拼接起来)

移位运算符:>>、