时间:2025-01-22 来源:FPGA_UCY 关于我们 0

4.-20K开发板上运行-M1软核处理器

4.1.适用于GoWin FPGA的ARM -M1 简介

ARM针对FPGA领域,利用EDA软件,对自家的-M0内核的源文件进行加密,使得在保护IP源代码知识产权的情况下,终端用户可以直接采用ARM -M0内核作为FPGA的复杂逻辑控制的处理器,此时FPGA里的-M0软核处理器就被命名为-M1。

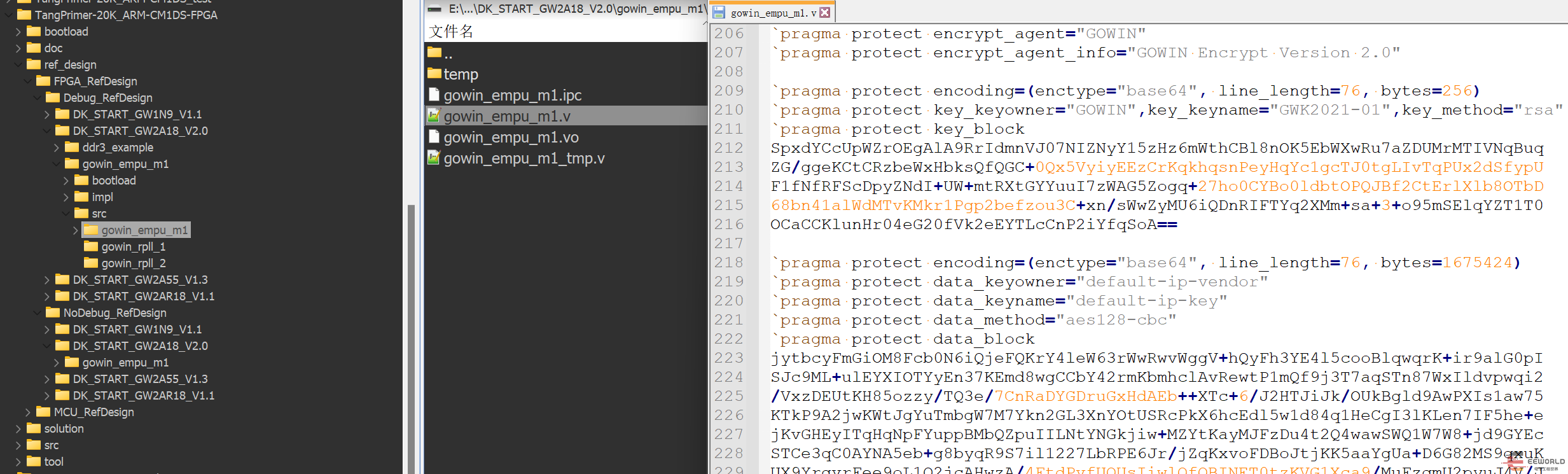

高云与ARM合作,将-M1内核,以及许多芯片内IP集成,形成一个完整功能的SoC,并以加密的形式发布,并提供了SoC的参考设计,从GoWin网站上下载 .6.5.zip ,解压后其内容结构以及加密后的M1内核源文件如图:

其中给出了两种不同配置-M1内核的SoC参考设计,一种带有JTAG/SW调试功能支持,另一种则不带。前者是后者的超集,包含了后者的功能,因此本实验主要采用前者,并在后续软件测试中,利用JTAG/SW的调试功能,实现代码下载、软件调试等。

4.2.FPGA软核SoC的构建

参考设计开发包针对GoWin官方的不同系列的几个开发板进行了适配,与本实验使用的-20K开发板接近的是.0。后续所有操作都是根据该开发板的项目文件来进行修改移植。

该开发板有两个适配项目,一个是,另一个是,出于简便考虑,先测试后者。

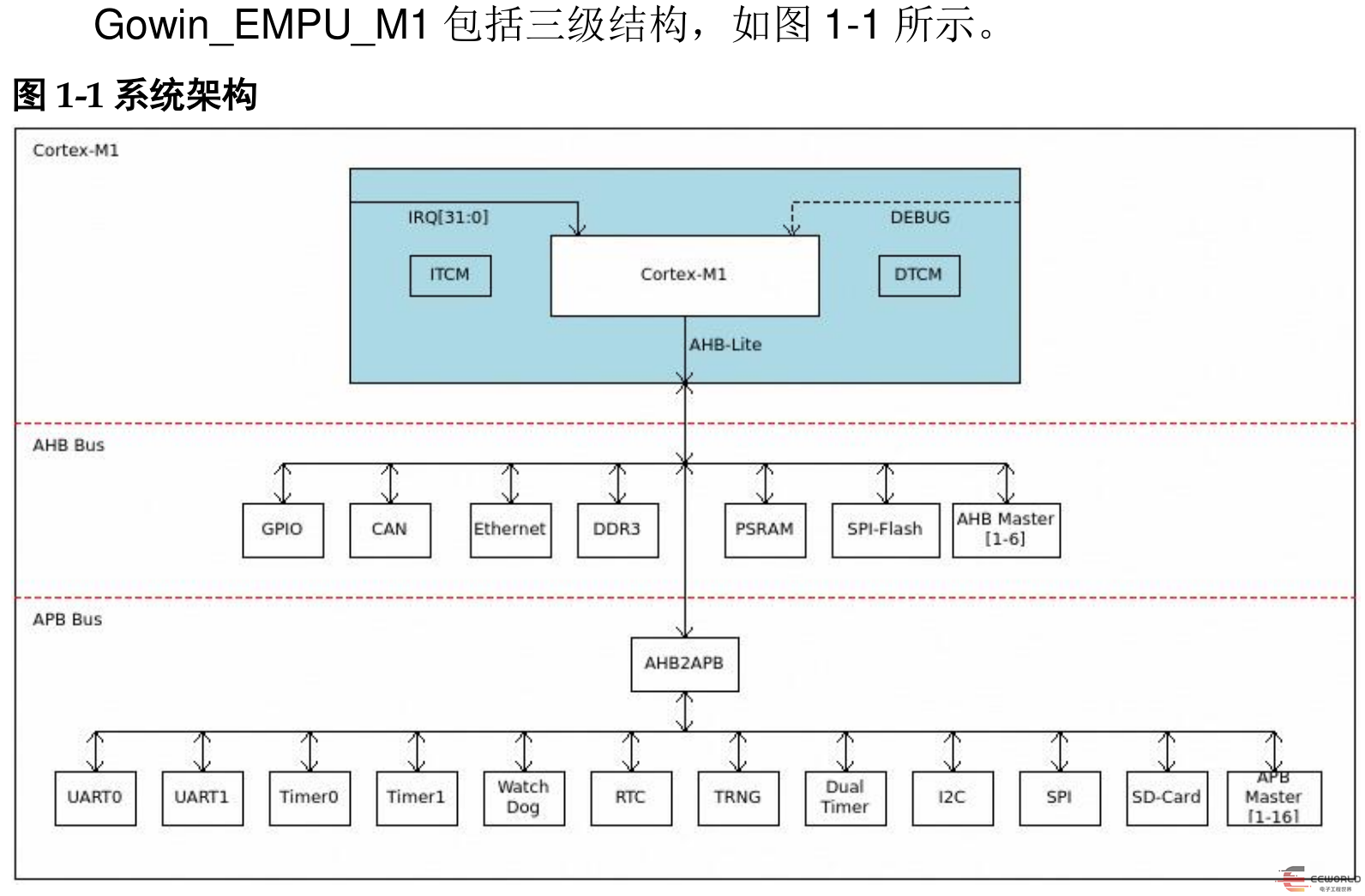

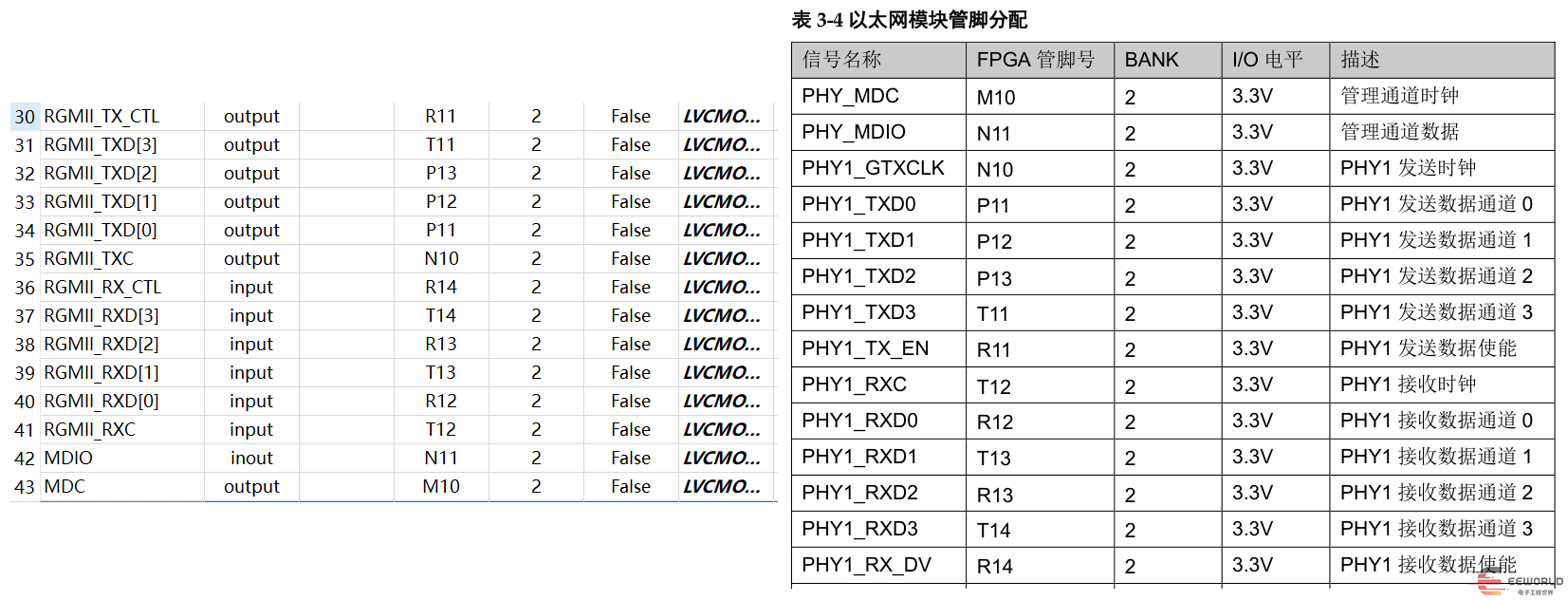

集成了多种IP核,包括GPIO、UART、I2C、SPI,以及(RGMII接口的)、SD卡(SPI模式)、等等,如图:

4.2.1.项目文件的概览与综合

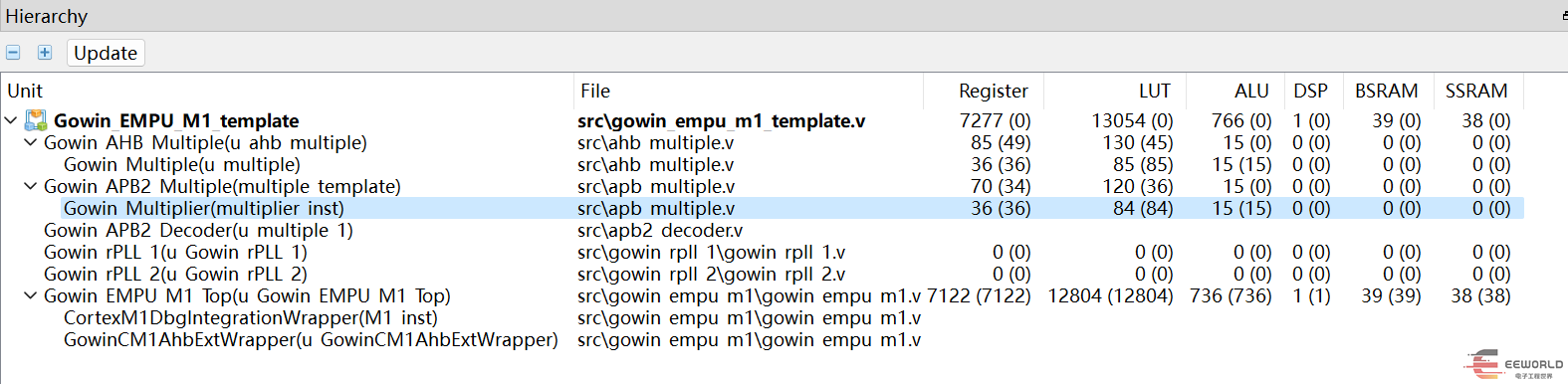

按照FPGA开发软件的流程,打开 .下的项目文件,可以看到项目层次结构,与对应的文件:

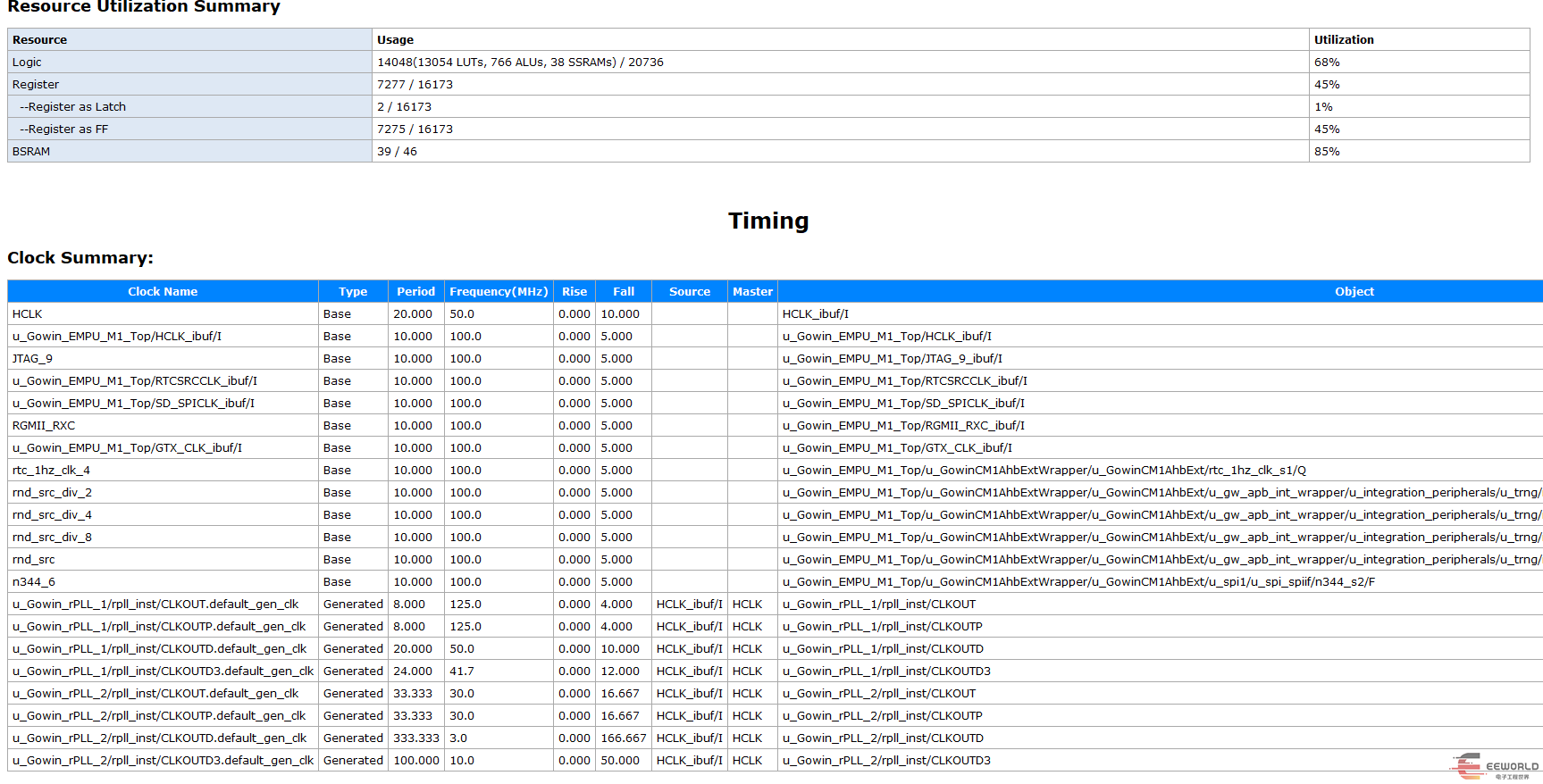

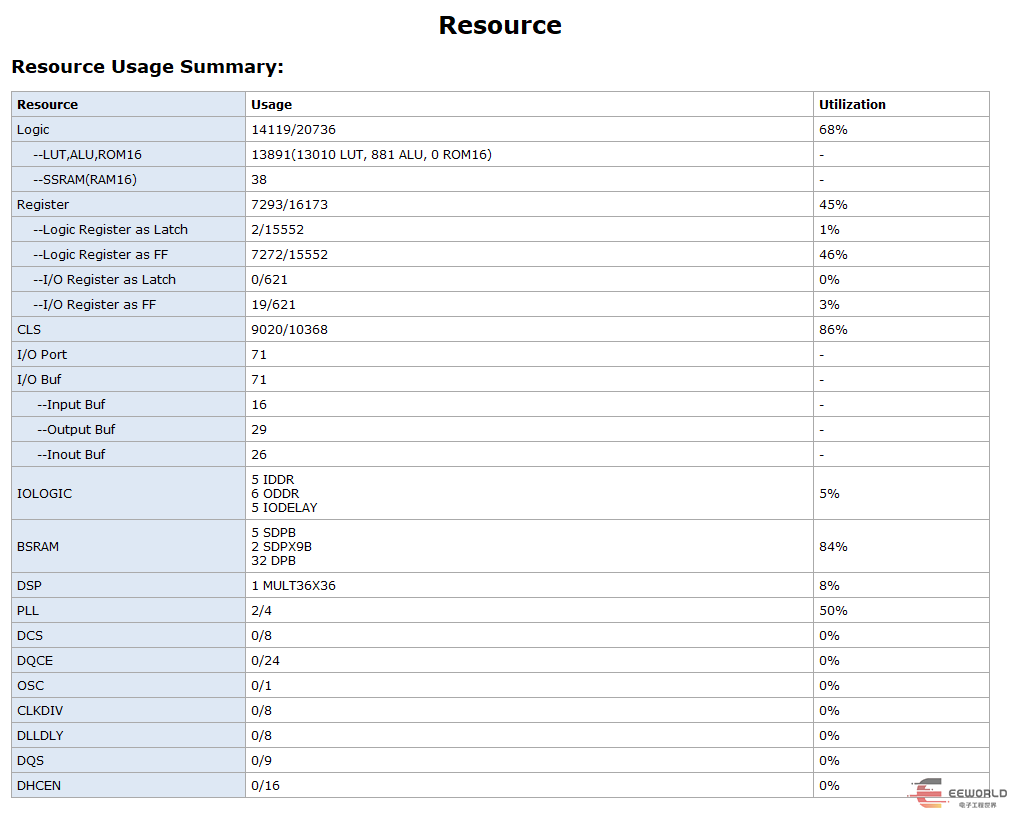

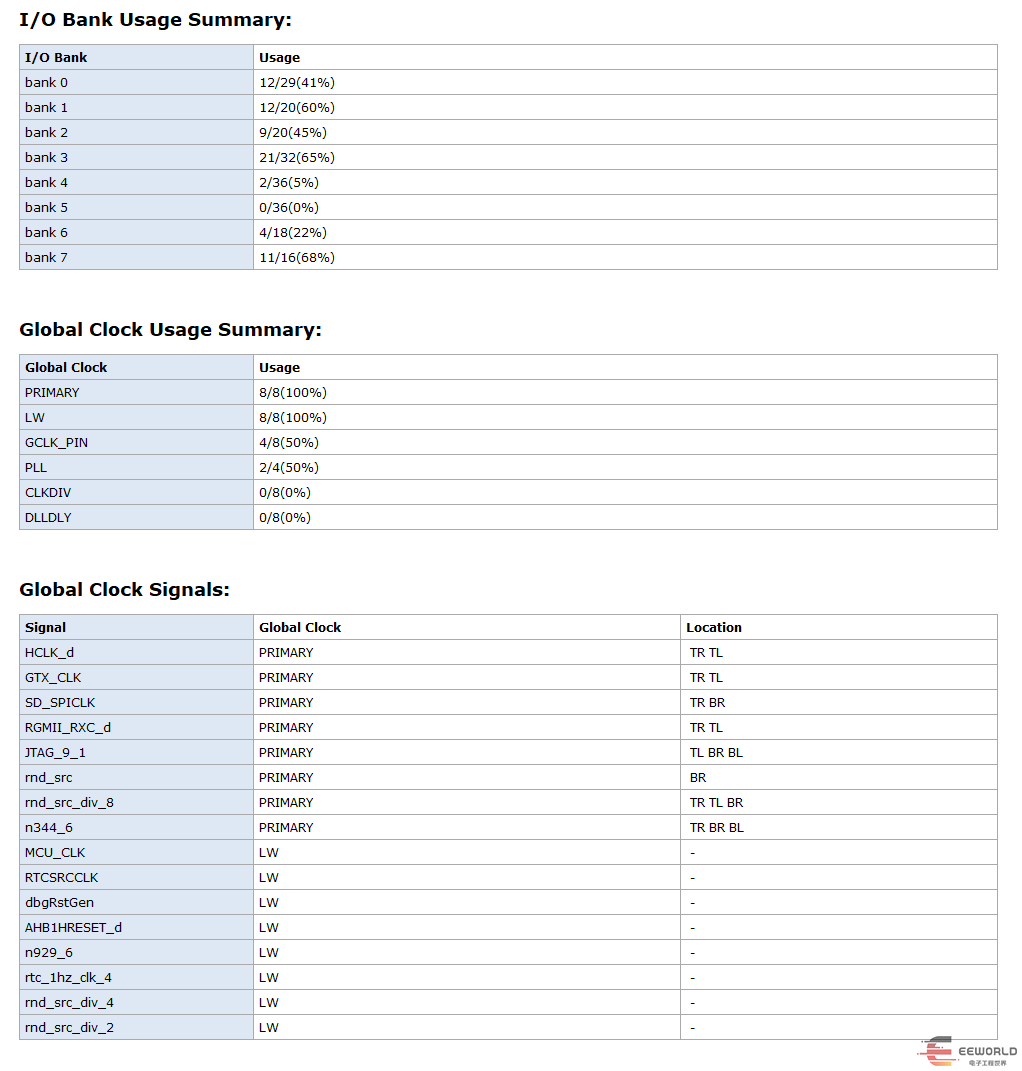

综合后,可以看到资源利用率和关键时钟信号:

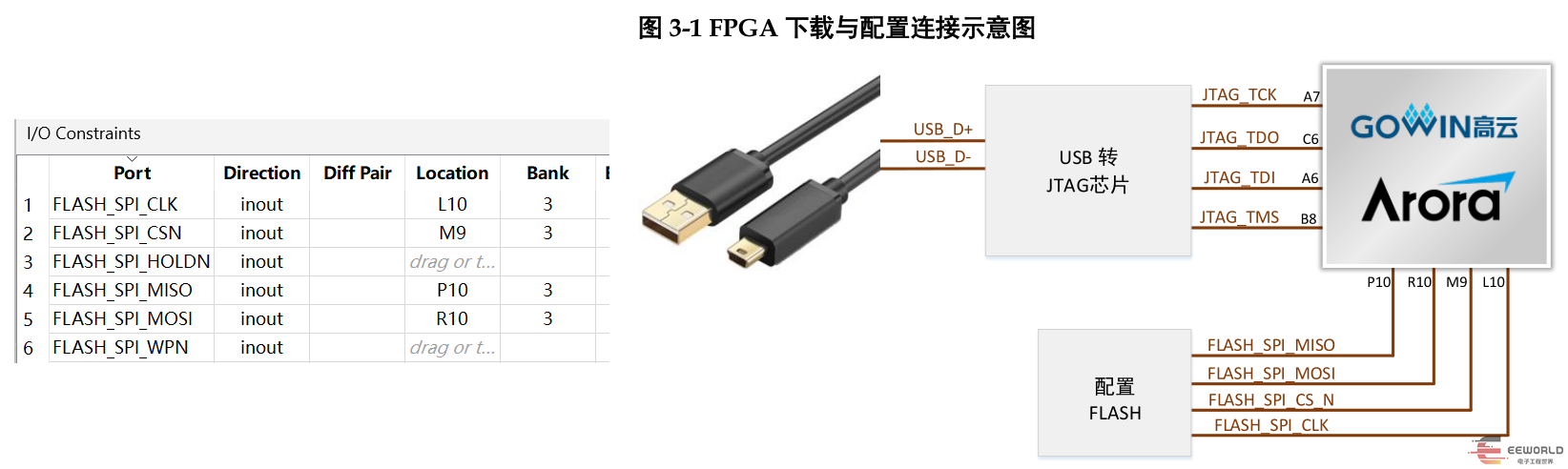

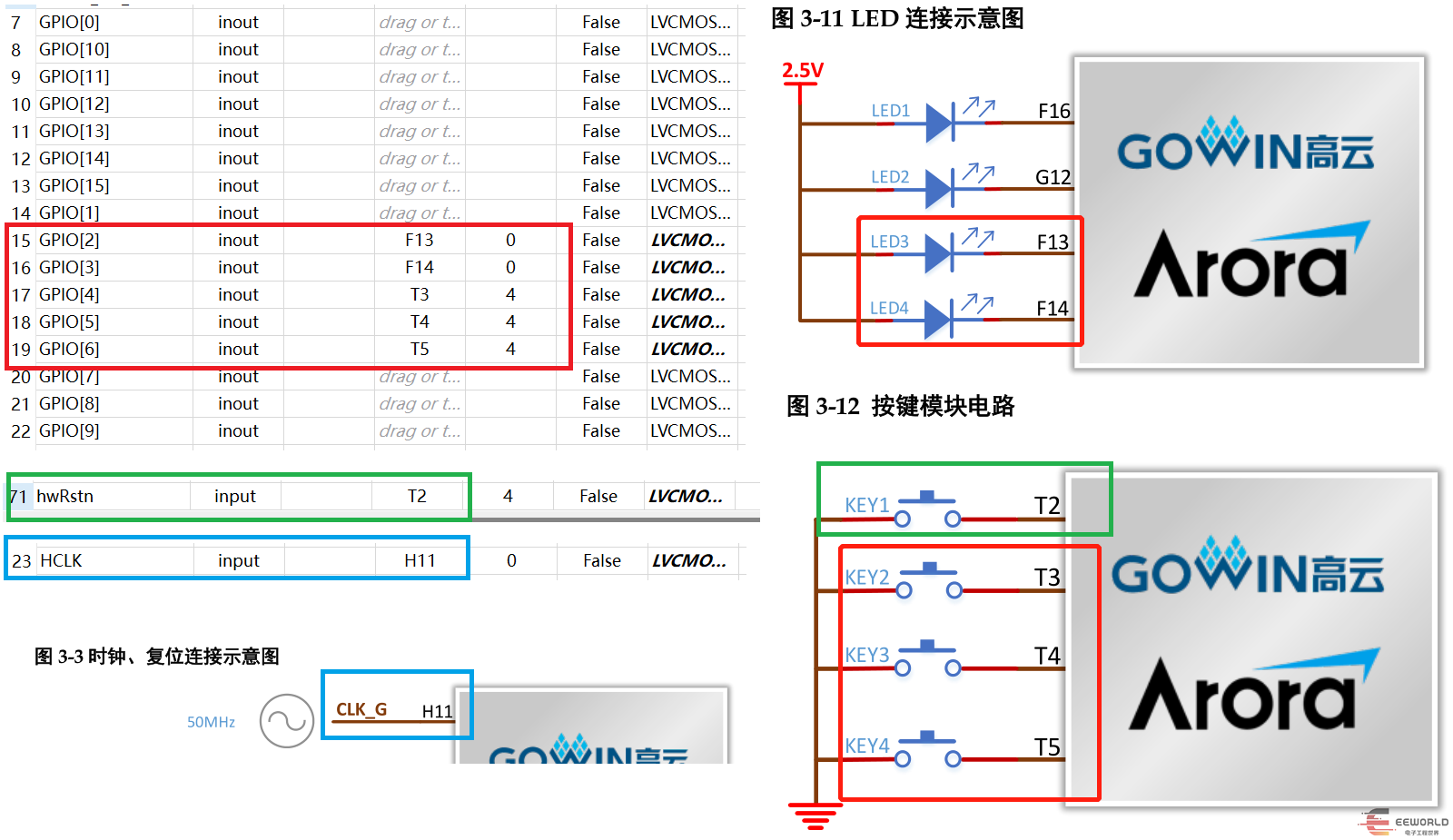

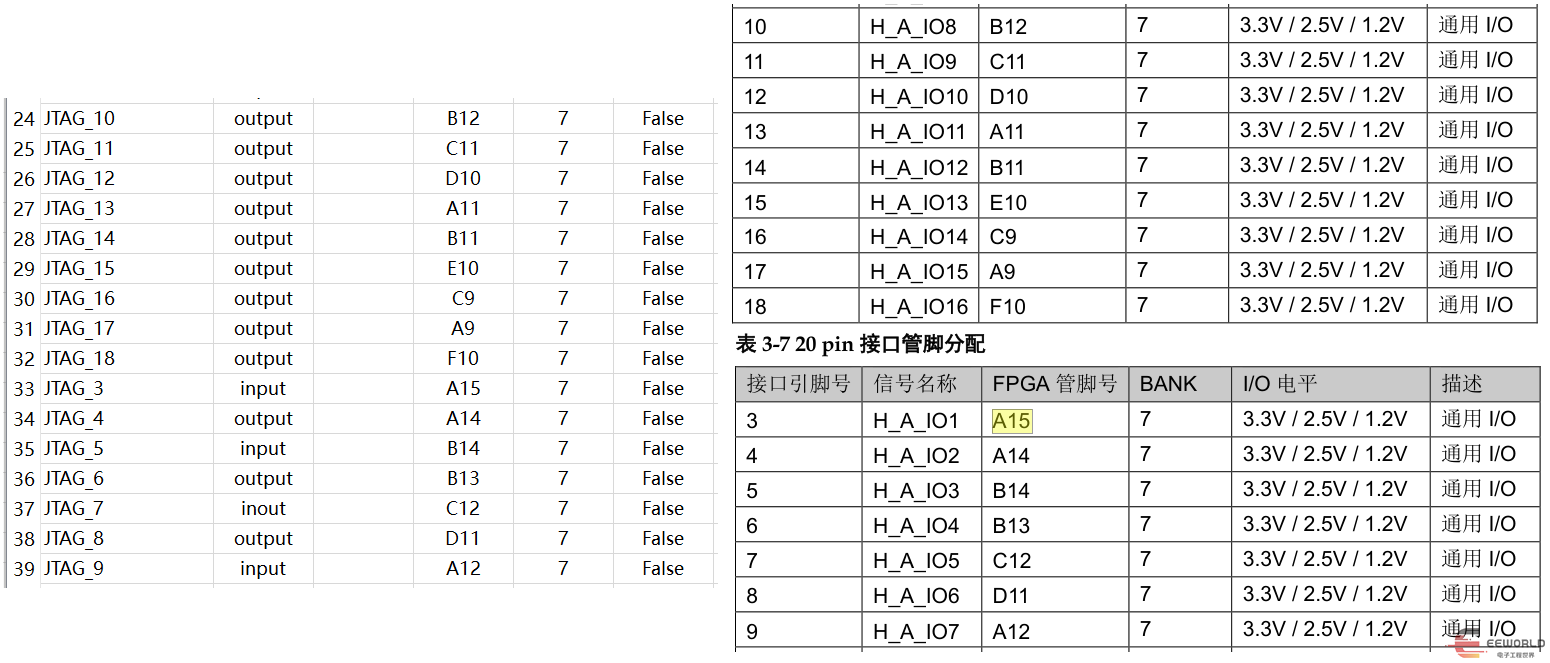

4.2.2.适配-20K开发板的IO引脚分配

打开,对引脚进行分配,由于原项目是针对开发板,配置的IO引脚也是跟该开发板匹配,如图:

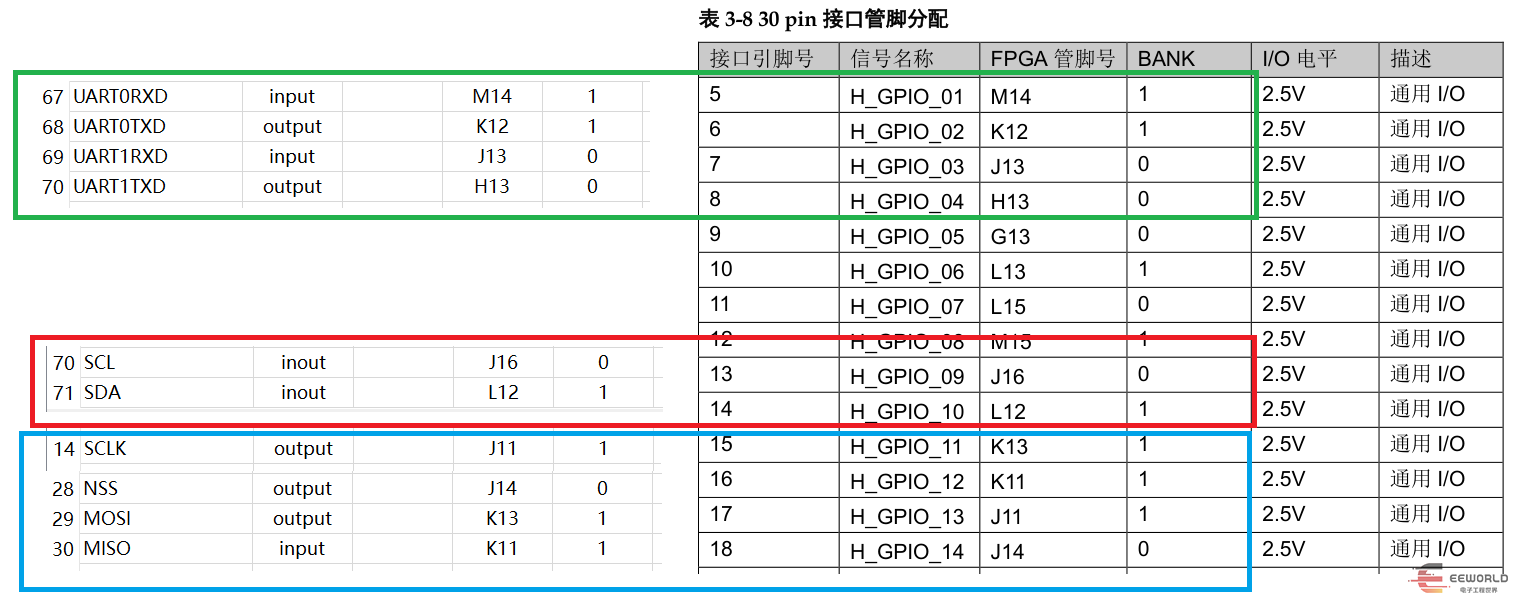

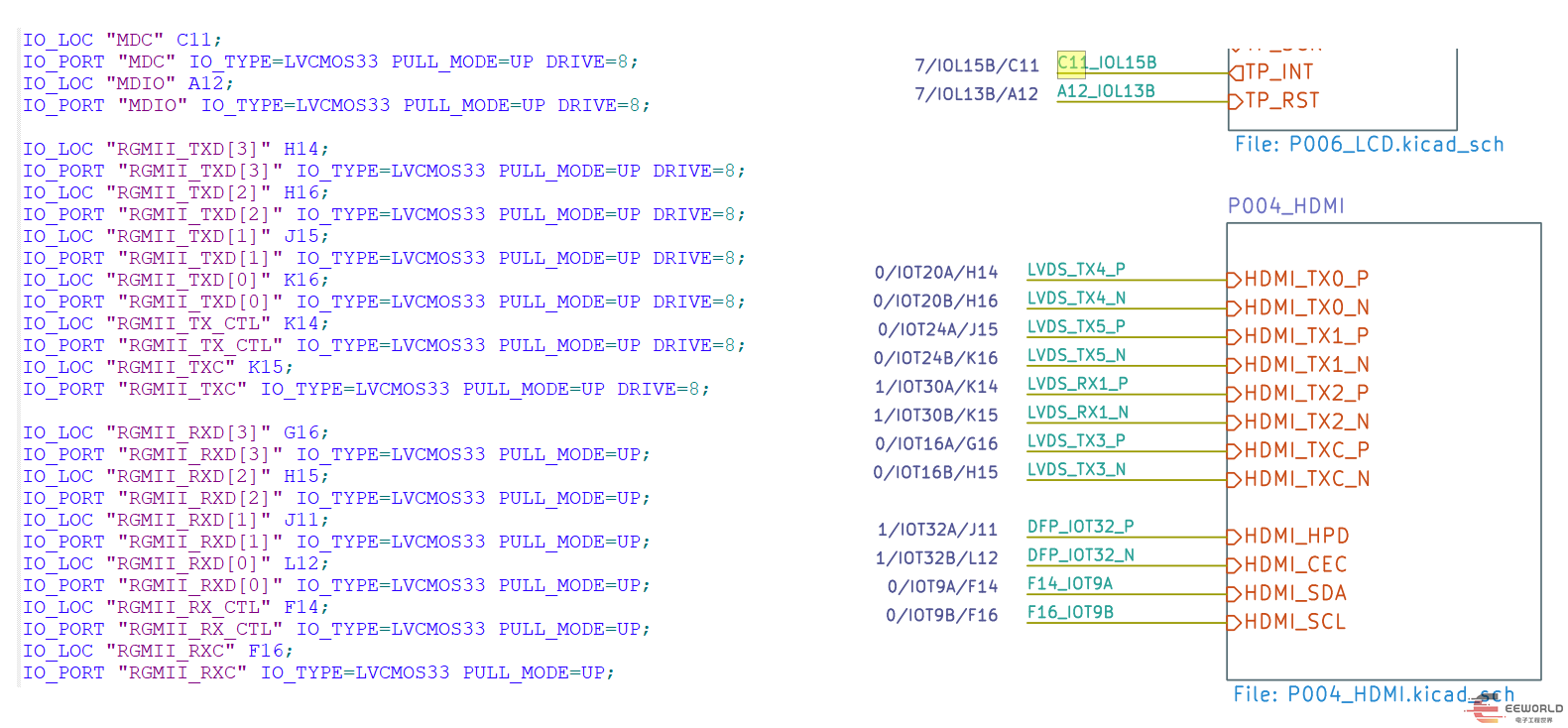

为了移植到本次实验用到的开发板(-20K+),根据FPGA项目中的引脚需求和-20K的板载硬件资源,除了项目中的RGMII接口无法满足外,其余均可连接至-20K对应的硬件资源中。其中:

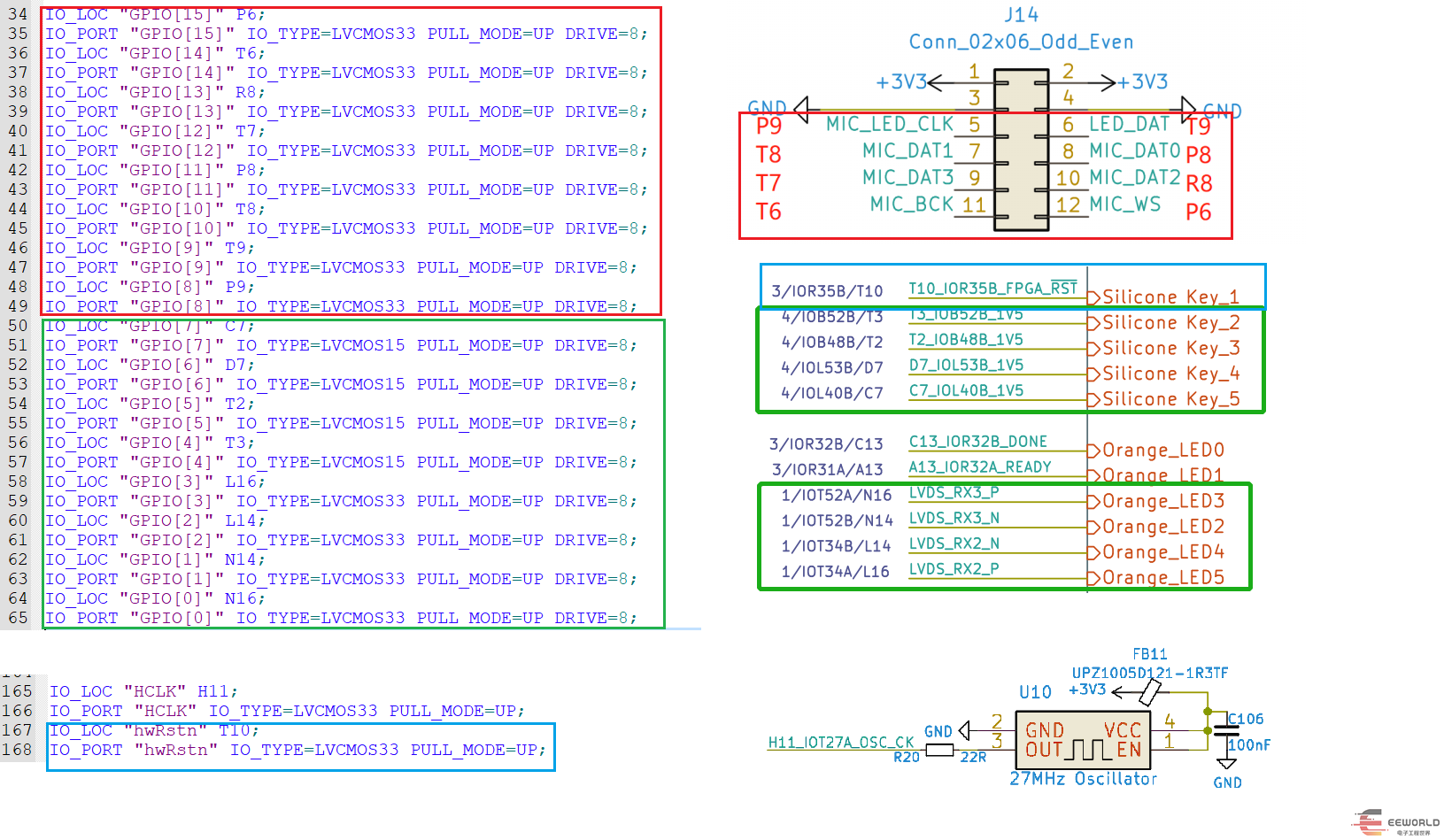

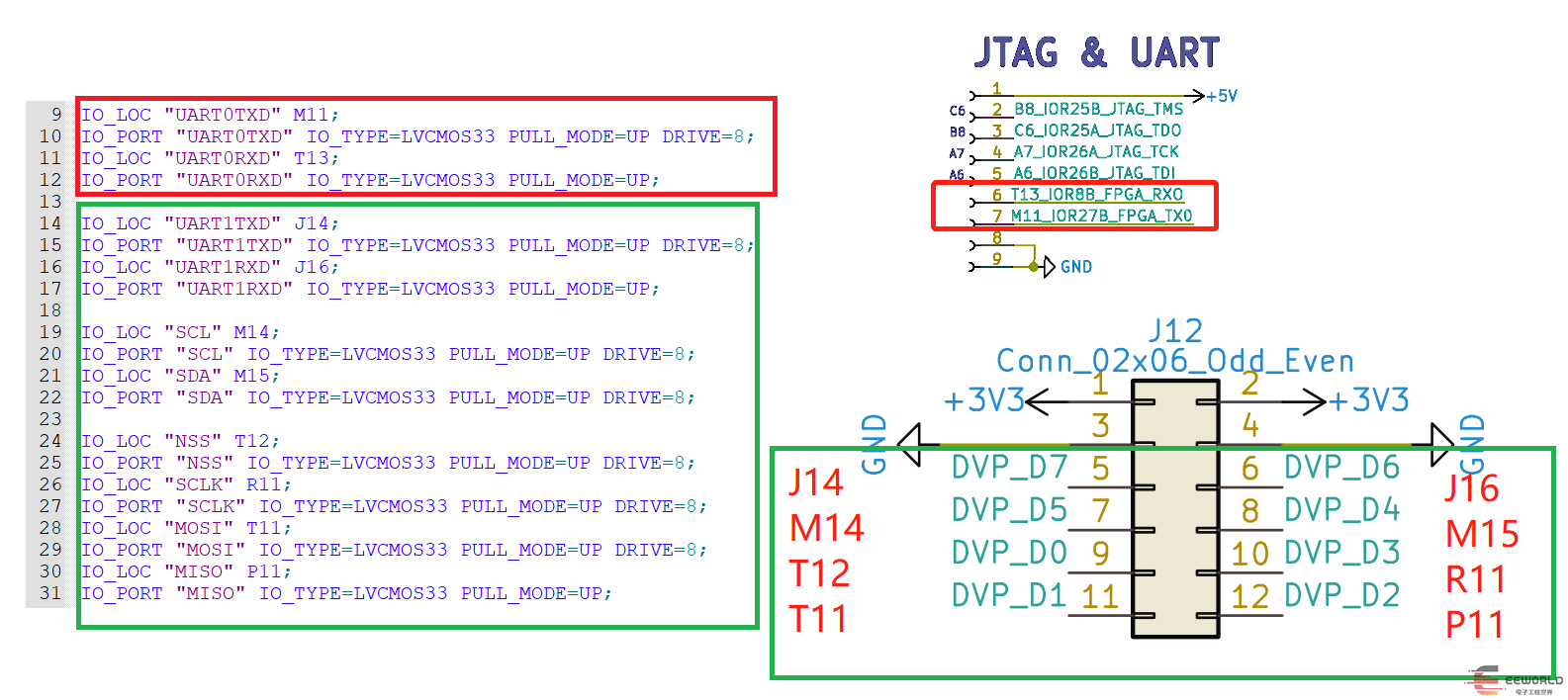

GPIO[3:0]分配到LED,GPIO[7:4]分配到S1~S4按键,GPIO[15:8]分配到2.54mm排母上;

rstn分配到按键S0,clk为板载27MHz;

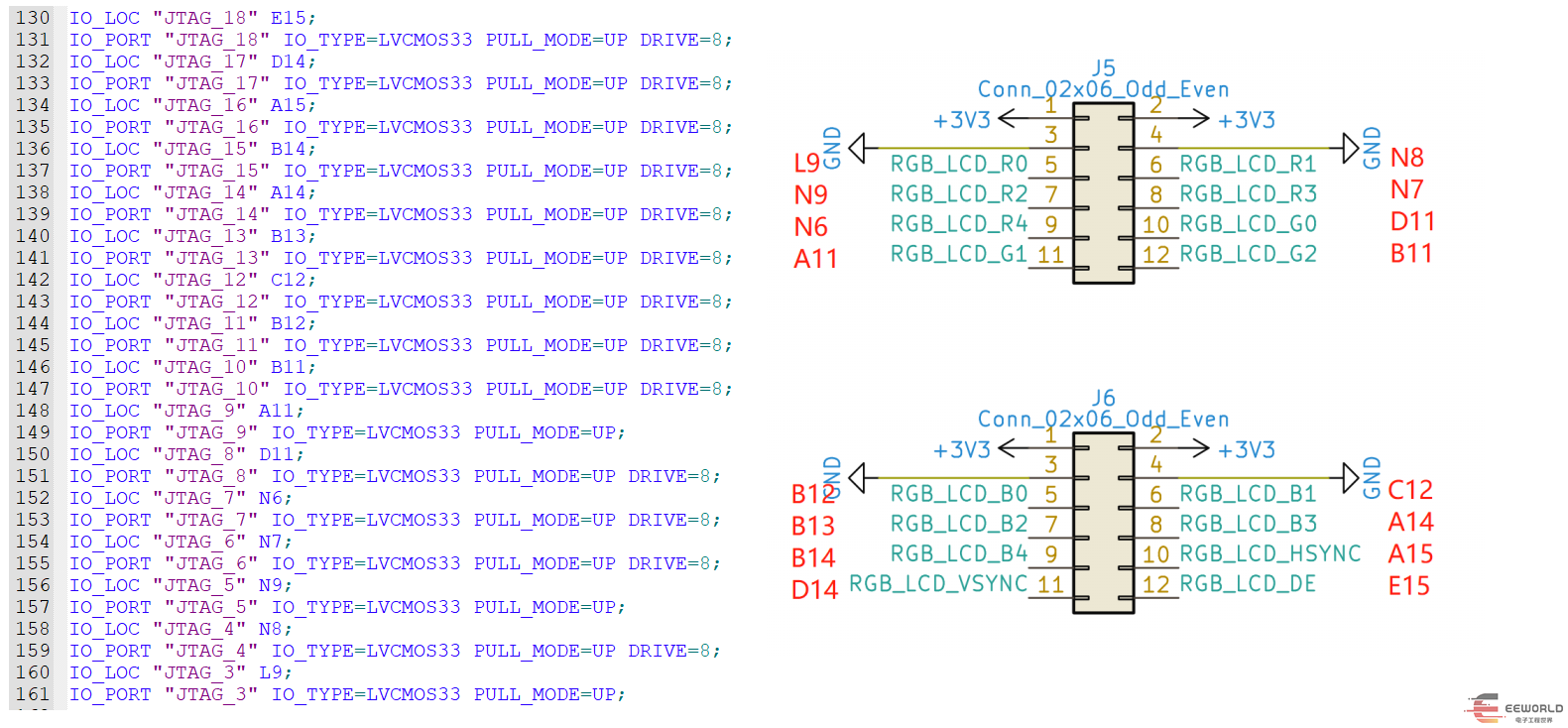

JTAG分配到2.54mm排母上。

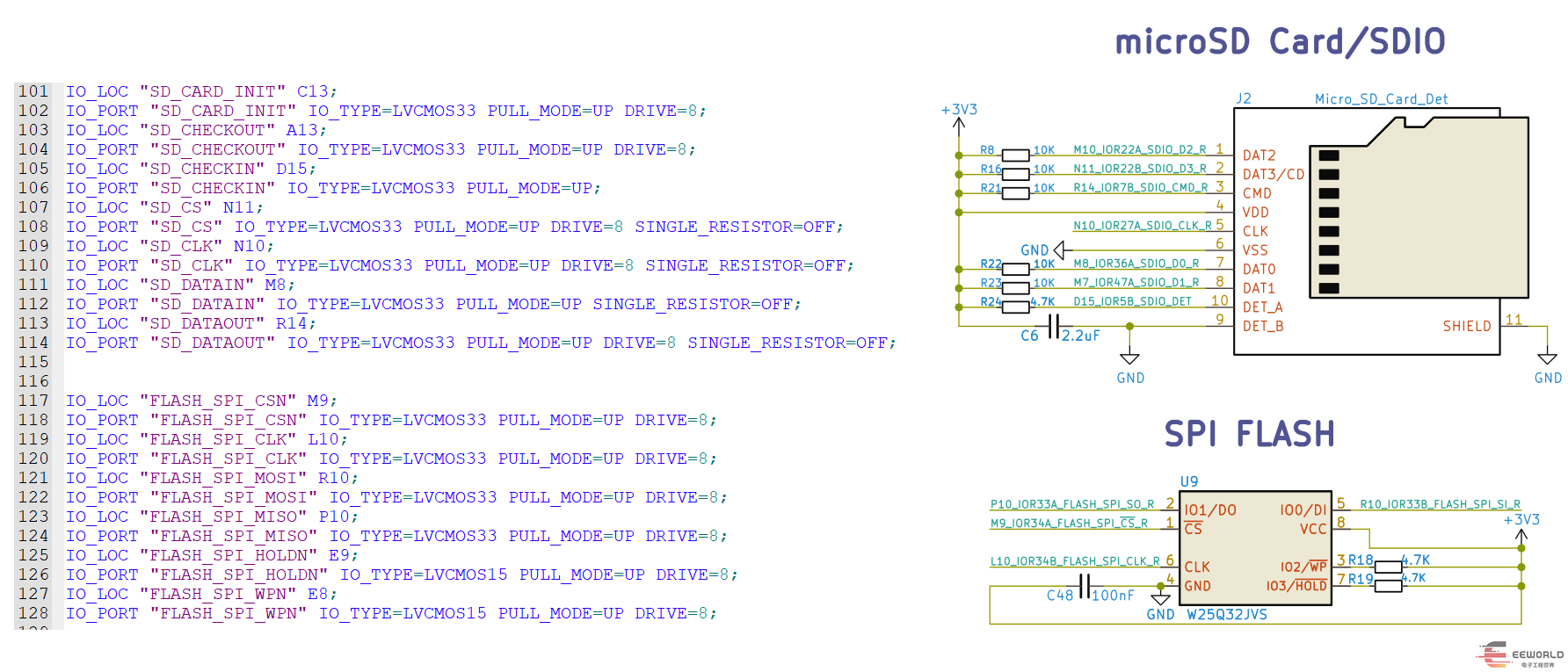

和spi-flash都分配到核心板上对应的信号,多出的几个信号分配到无关的LED/IO引脚;

RGMII相关信号分配到底板的HDMI接口上,并确保HDMI接口留空,避免信号冲突;

UART0分配到底板调试器的UART上,UART1、I2C、SPI分配到2.54mm排母上。

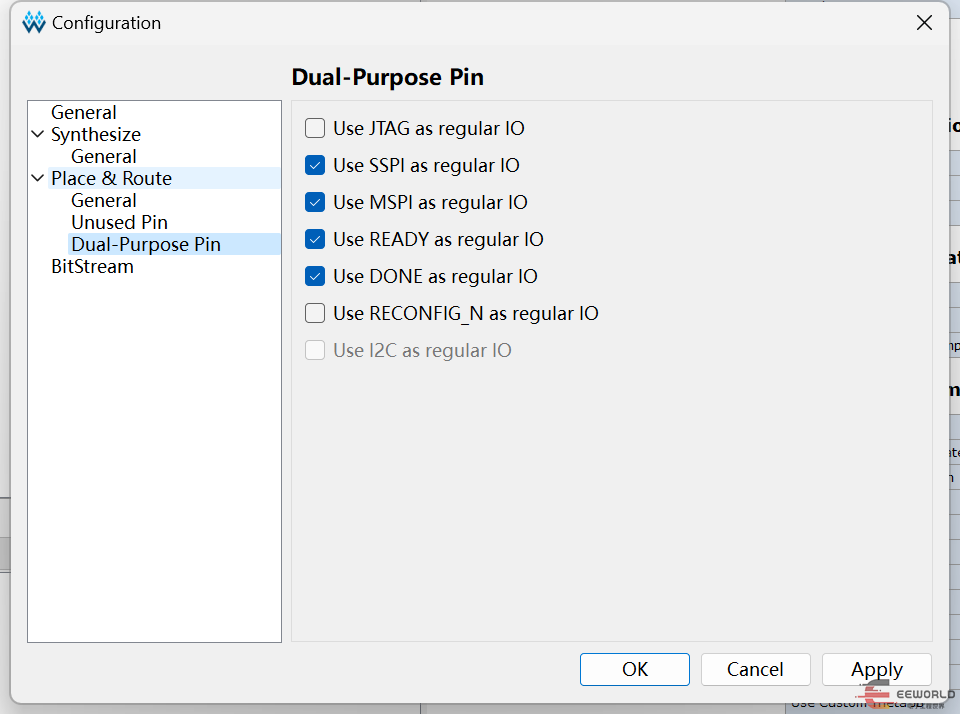

同时需要在菜单栏的->中,设置SSPI、MSPI、READY、DONE等多功能引脚作为通用IO引脚功能:

4.2.3.FPGA项目的编译与下载

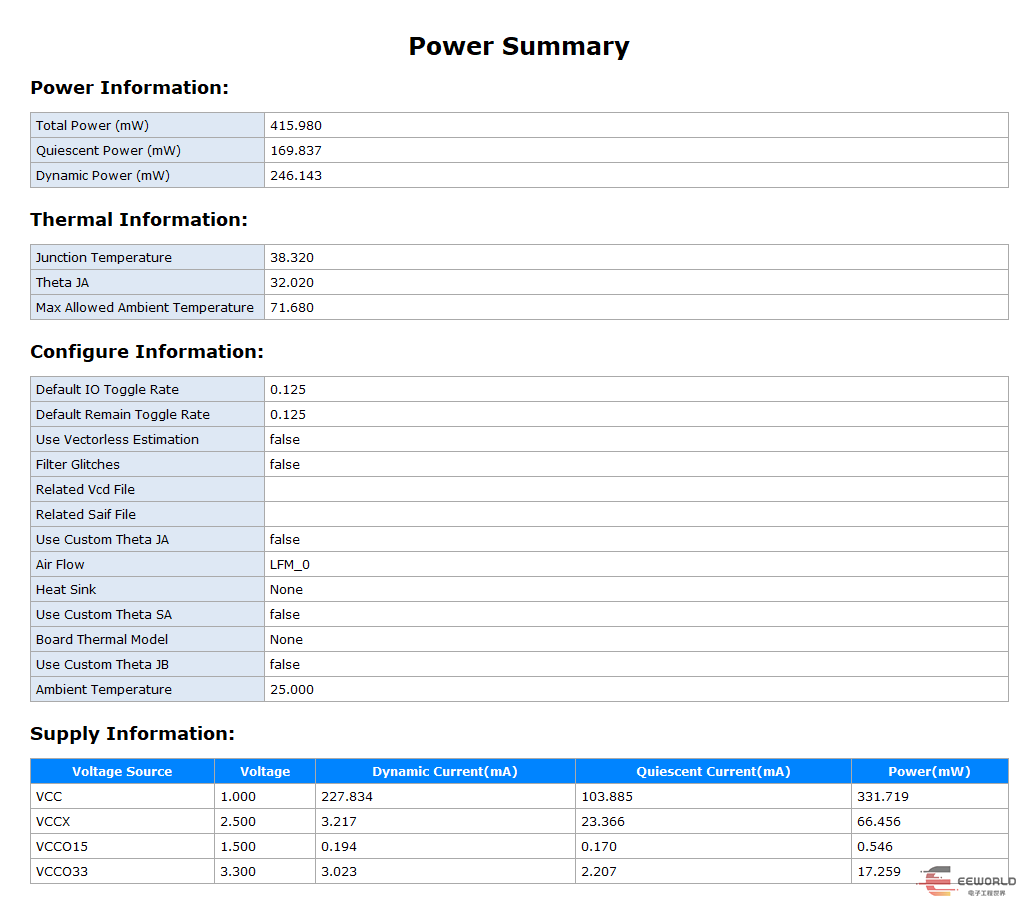

按照EDA软件的编译流程,完成布局布线、时序、功耗分析,最终生成文件。各项流程报告如下:

使用软件下载到FPGA,由于没有软件代码,-M1内核处于异常状态,开发板无运行输出。

4.3.Keil软件开发和下载调试_led例程

选用的是带有JTAG/SW调试接口的-M1软核,因此可以使用Keil等开发工具进行在线代码下载、调试。

4.3.1.JLink调试器的连接与识别

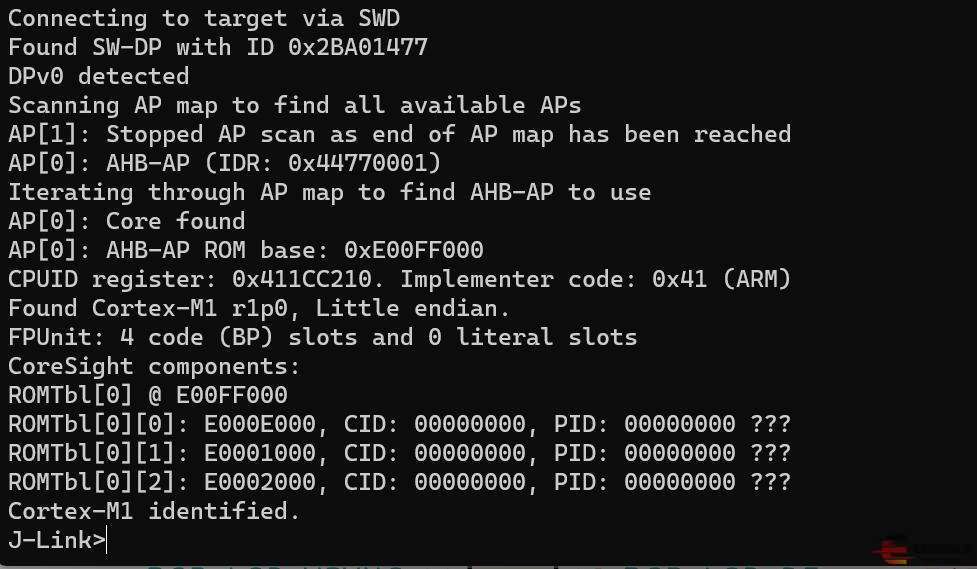

采用JLink-OB作为调试器,连接到JTAG7(SWDIO)和JTAG9(SWCLK),和GND共三根信号线,连接后使用JLink-可以识别出ARM -M1内核:

4.3.2.Keil项目的设置、编译、下载与调试

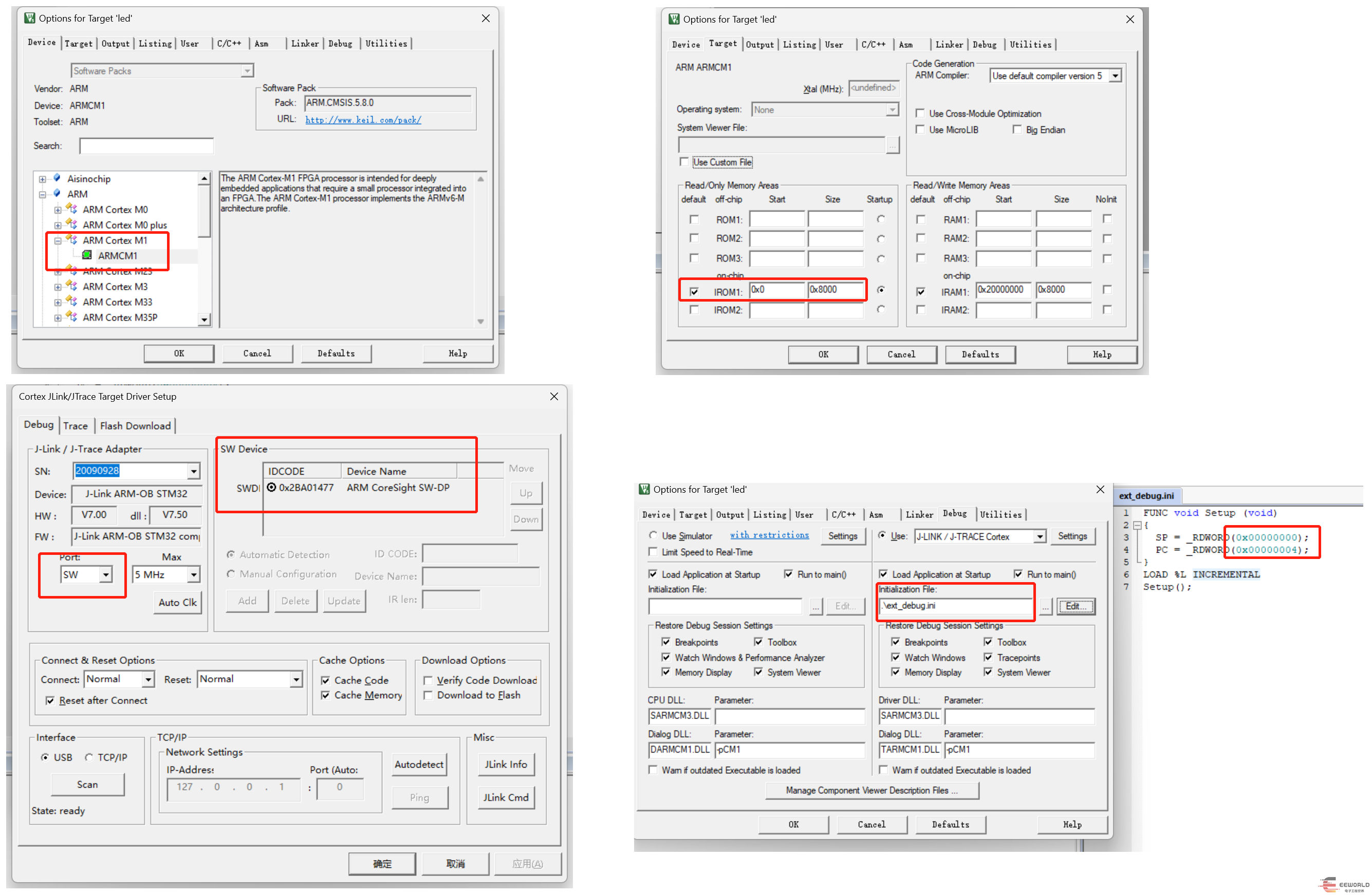

使用Keil软件打开///led//led.,按照文档说明,由于本设计采用的是片内ITCM和DTCM,因此应改为对应的地址,如图:

调试初始化文件.ini中,也应改为对应的地址:

FUNC void Setup (void)

{

SP = _RDWORD(0x00000000);

PC = _RDWORD(0x00000004);

}

LOAD %L INCREMENTAL

Setup();

为适配-20K板载的27MHz时钟频率,需要将软件代码中,.c文件中的改为,如下:

/*---------------------------------------------------------------------------- Define clocks *----------------------------------------------------------------------------*/ #define XTAL (100000000UL) /* Oscillator frequency */ // #define SYSTEM_CLOCK (XTAL / 2U) /* 50MHz */ #define SYSTEM_CLOCK (27000000) /* 27MHz */

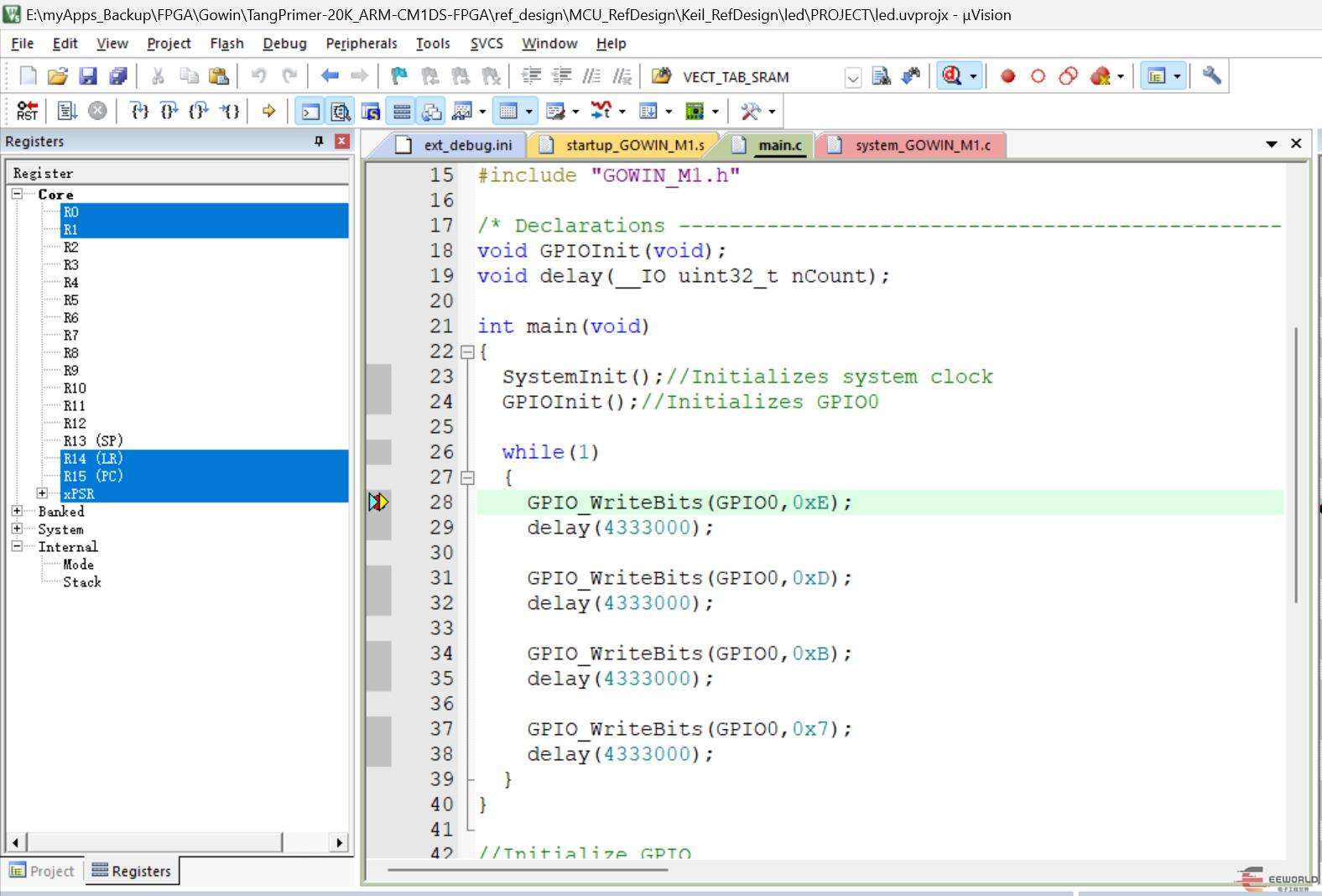

在Keil软件中开启Debug,Keil软件读取.ini并执行代码的下载,和SP、PC寄存器的初始化,然后可以设置断点,运行、单步调试等操作:

4.3.3.运行效果

运行效果如下:

本文来自论坛,点击查看完整帖子内容。