时间:2025-01-13 来源:FPGA_UCY 关于我们 0

FPGA时序分析基础知识总结

下面将FPGA时序分析涉及到的基础知识总结如下。

时序分析目的

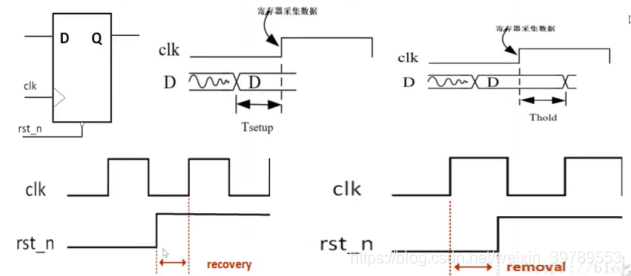

时序分析的本质是一种时序检查,目前是检查FPGA中所有的D触发器能否正常工作,也就是检查D触发器的同步输入的数据端口是否满足建立时间(setup time)和保持时间(hold time)的要求。

还有一个容易忽略的就是D触发器的异步复位端口是否满足恢复时间( time)和移除时间( time)要求。

时序分析工具

静态时序分析工具有:

1、

2、 II

3、DC

动态时序分析工具有:

1、

2、 NC-

3、 VCS

时序分析分类

时序分析分为动态时序分析和静态时序分析。

1、动态时序分析:可以理解为类似于我们用进行的时序仿真分析。主要原理是将布局布线的延迟信息反标到网表文件中进行仿真分析,检查是否存在时序违例,此时的延时包括门延时和布线延迟,可以很好地反应芯片的实际工作状态。

因为不能生成完备的测试向量,覆盖所有的网表路径,因此在动态时序仿真分析中,无法暴露一些路径上可能出现的时序违例问题。

2、静态时序分析:采用穷尽分析方法来提取整个电路存在的所有时序路径,计算信号在这些路径上的传播延时,检查信号的建立和保持时间是否满足时序要求,找出违背时序约束的错误。它不需要输入向量就能穷尽所有的路径,且运行速度很快、占用内存较少,不仅可以对芯片设计进行全面的时序功能检查,而且还可利用时序分析的结果来优化设计。

时序分析前提

撰写基本的时序约束文件,告知时序引擎一些必要的信息(比如时钟,输入输出延时等)。若没有正确的时序约束,那么时序分析的结果是没有意义的。

时序分析常用术语

1、源寄存器:发起数据的寄存器;

2、目的寄存器:捕获数据的寄存器;

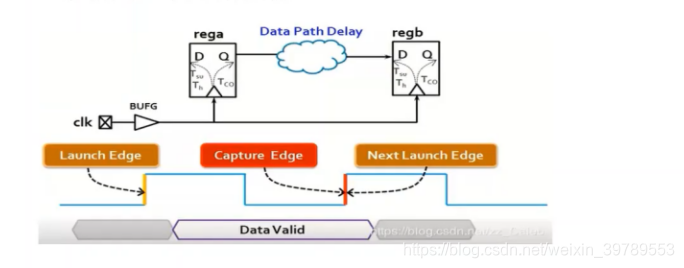

3、源时钟( clock/ clock):也称发起时钟;

4、目的时钟( clock/ clock):也称捕获寄存器;

5、发起沿( edge):源时钟产生数据的有效时钟沿;

6、捕获沿( edge):目的时钟捕获数据的有效时钟沿;

7、发起沿通常在0ns,捕获沿通常在下一个发起沿,捕获沿与发起沿“通常”相差1个时钟周期,注意这个通常加了引号,因为源时钟与目的时钟不一定为同一个时钟,这点需要特别注意。

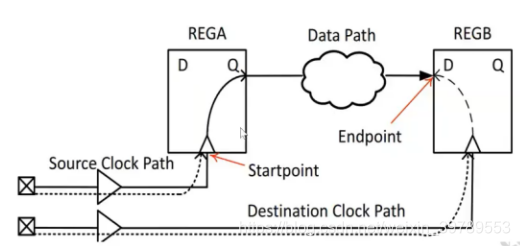

时序路径的三要素

1、源时钟路径:从源时钟的源节点(一般为FPGA的时钟输入引脚)到源寄存器的时钟输入端的路径,当输入数据的时序路径的起点为FPGA的输入引脚时,则没有源时钟路径。

2、目的时钟路径:从目的时钟的源节点(一般为FPGA的时钟输入引脚)到目的寄存器的时钟输入端的路径,当输出数据的时序路径的终点是FPGA的输出引脚时,则没有目的时钟路径。

3、数据路径:从时序路径的起点到时序路径的终点之间经过的数据路径,时序路径的起点一般为源寄存器的时钟输入端口(因为数据实在源寄存器时钟输入端口的发起沿时刻将数据发送出去的)或者FPGA输入引脚;时序路径的终点一般为目的寄存器的数据输入端口或者FPGA的输出引脚。