时间:2024-08-09 来源:网络搜集 关于我们 0

上期内容:时序约束是如何影响Vivado编译时间的

本文关注点:

时钟管脚的差异时钟区域的差异时钟缓冲器的差异时钟是整个FPGA设计的“发动机”,FPGA内部逻辑正是在时钟的驱动下运作,因此,管理好时钟拓扑结构尤为重要,而时钟的拓扑结构又与相应的具体芯片型号相关。

这里我们介绍一下UltraScale系列FPGA与7系列FPGA在时钟资源方面的主要差异。

时钟管脚7系列FPGA的时钟管脚分为SRCC(Single-region clock-capable I/O)和MRCC(Multi-region clock-capableI/O),两者的主要差异在于驱动局部时钟资源的类型不同,也就是SRCC可驱动BUFR,不能驱动BUFMR,而MRCC则即可驱动BUFR也可驱动BUFMR。在UltraScale系列FPGA中,GC(Global Clock)管脚取代了SRCC和MRCC,换言之,GC不再有SRCC和MRCC。

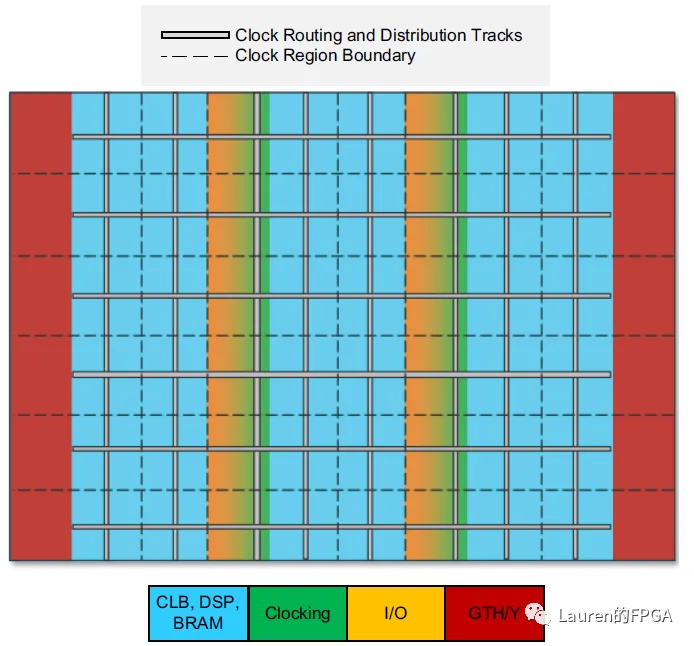

时钟区域这里所说的时钟区域(Clock Region)是FPGA内部结构,包括相应的CLB、DSP、BRAM、互联资源等。7系列FPGA中,时钟区域的宽度(水平方向)为芯片宽度的一半,而UltraScale不再有这种限制。如下图所示的UltraScale时钟区域(图片来源,ug949,figure3-37),共有6x6即36个,如果是7系列FPGA,则是2x6即12个。

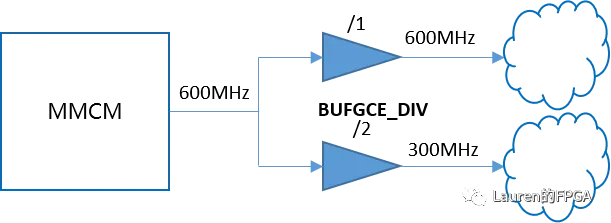

时钟缓冲器7系列FPGA中有所谓的局部时钟缓冲器,例如BUFR、BUFMR、BUFIO等,而UltraScale系列FPGA中不再包含这类时钟缓冲器,其功能由新增的BUFGCE_DIV代替。同时,需要明确BUFGCE_DIV并非局部时钟资源,而是全局时钟资源。BUFGCE_DIV具有分频功能,对于简单的分频,相比于MMCM/PLL,BUFGCE_DIV在功耗上更具优势,而且如果分频时钟和源时钟有跨时钟域路径,那么相应的Clock Skew会更小。看一个案例,设计中需要两个时钟,一个600MHz,一个300MHz,可采用如下图所示方案。MMCM生成时钟为600MHz,实例化两个BUFGCE_DIV,其分频因子分别为1和2,从而可分别生成一个600MHz时钟和一个300MHz时钟,而且,这两个生成时钟也是同相的。

此外,在使用高速收发器生成的时钟时,可以使用BUFG_GT。该时钟缓冲器也具有分频功能,也可以驱动FPGA内部其他逻辑资源。

此外,在使用高速收发器生成的时钟时,可以使用BUFG_GT。该时钟缓冲器也具有分频功能,也可以驱动FPGA内部其他逻辑资源。

文 | Lauren 图 | Lauren