正弦波发生器是大多数数字信号处理系统内的主要元件,通常称为直接数字综合器(DDS)或数控振荡器(NCO)。常用于构建数字上下转换器、解调器和实现各种类型的调制方案,包括PSK(相移键控)、FSK(频移键控)和MSK(最小移键控)。

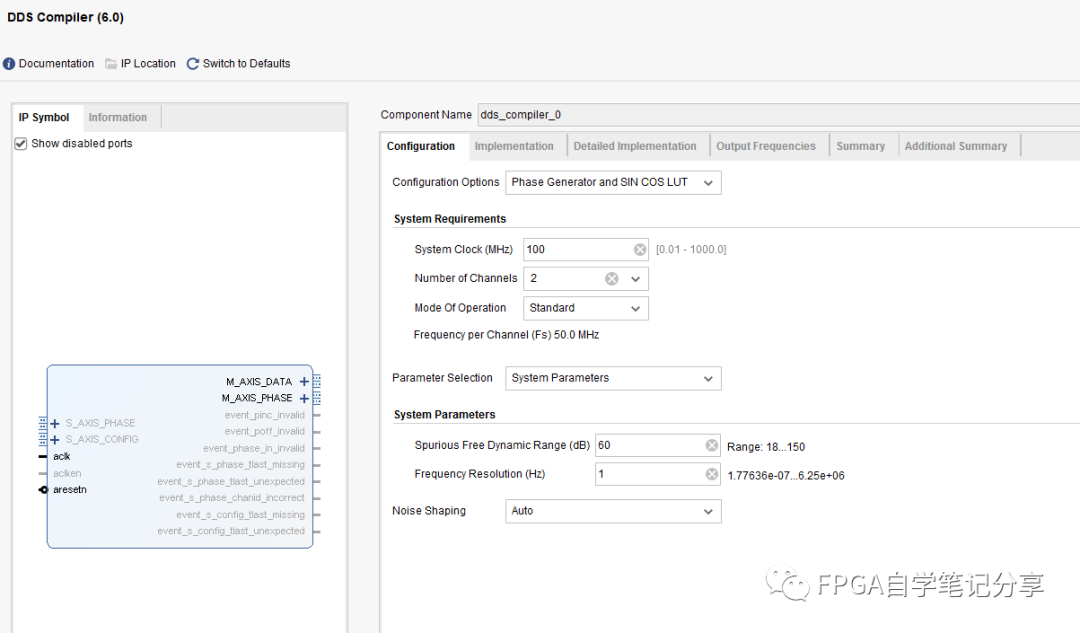

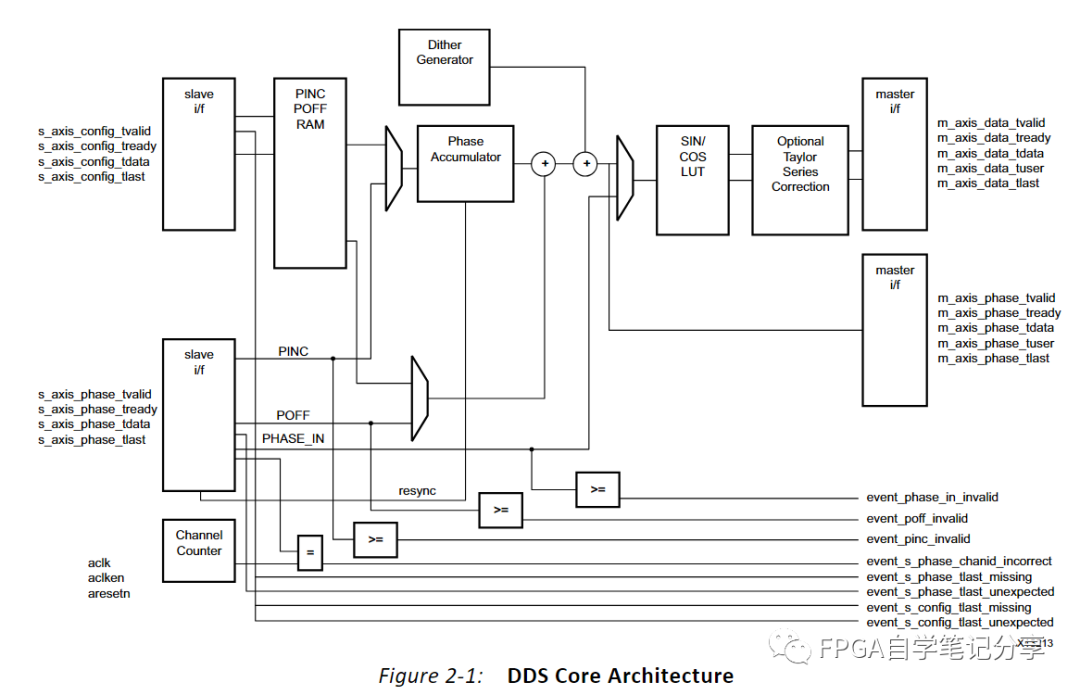

尽管DDS 函数在算法上很简单,但它们给硬件设计人员在实现函数时带来了巨大的挑战。例如,可能难以限制满足高 SFDR 要求或实现器件的最大时钟性能所需的内存量。通过利用XILINX的DDS Compiler IP,这些问题将得以解决,实现时只需图形化界面中点击一下即可。此外,ip还允许用户权衡DSP RAM LUT0等资源,以获得最适合其系统的解决方案。XILINX DDS Compiler IP的特性为:Phase 和 SIN/COS 值可以单独/同时生成栅格化特征消除了截位带来的相位噪声正弦、余弦或方波输出每个通道的累积相位重新同步(可选)分布式或块 RAM资源可选可选的相位抖动分散谱线能量以获得最大 SFDR(无杂散动态范围)相位抖动或泰勒级数校正选项使用最少的 FPGA 资源提供宽动态范围信号SFDR:18dB 至 150dB多达 16 个时分通道高达 48 位相位累加器(DSP 切片或 FPGA 逻辑)的低频分辨率3 位到 26 位带符号输出采样精度数字生成复数或实值正弦波的常用方法采用查找表方案。查找表存储了正弦波的样本。数字积分器用于生成合适的相位参数,该相位参数通过查找表映射到所需的输出波形。之前的文章:FPGA数字信号处理之verilog实现NCO(原理)及FPGA数字信号处理之verilog实现NCO(代码及仿真)对查找表实现DDS的原理进行了详细的说明,XILINX DDS Compiler IP的结构如下,可以看到该IP同样使用查找表的方法进行波形生成。

XILINX DDS Compiler IP

支持如下三种输出模式

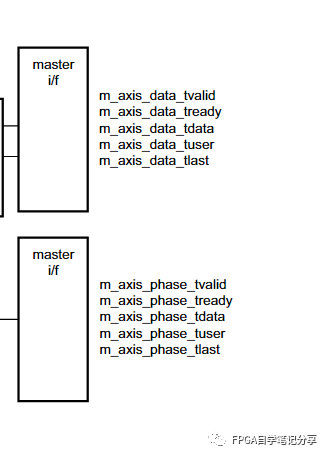

Phase Generator and SIN/COS LUTPhase Generator onlySIN/COS LUT only分别对应结构图上的m_axis_data和m_axis_phase接口如下图,Phase Generator and SIN/COS LUT模式时,m_axis_data和m_axis_phase接口同时存在分别输出COS/SIN值和相位值;Phase Generator only模式时,只有m_axis_phase接口存在输出相位值;SIN/COS LUT only模式时,只有m_axis_data接口存在输出COS/SIN值。

本文对XILINX FPGA的DDS Compiler IP的特性先做一个简单的说明,后续对各个模式及使用进行详细的探讨,详细的讲解可以看B站视频:【FPGA IP之DDS Compiler使用1_祝大家端午安康】 https://www.bilibili.com/video/BV1414y127E4/?share_source=copy_web&vd_source=9736f43bc2eebc284f4fbbe5805247a7

注明:本内容来源网络,不用于商业使用,禁止转载,如有侵权,请来信到邮箱:429562386ⓐqq.com 或联系本站客服处理,感谢配合!