本节目录

一、配置数据文件格式1、文件格式差异2、FPGA比特流内容3、位交换二、配置时序步骤1、步骤一:设备通电2、步骤二:清除配置内存3、步骤三:采样模式引脚4、步骤四:同步5、步骤五:检查设备ID6、步骤六:加载配置数据帧7、步骤七:冗余循环检查8、步骤八:启动

本节内容

一、配置数据文件格式

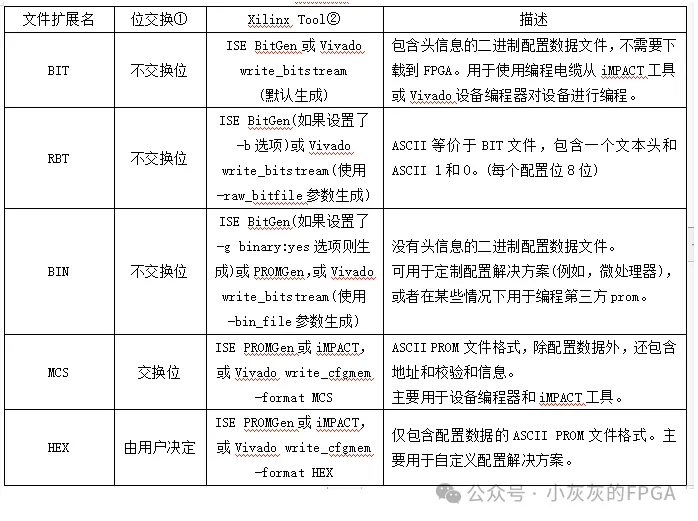

7系列的FPGA配置数据文件格式,有五种文件格式,BIT、RBT、BIN、MCS和HEX。对于FPGA开发工作者来说,使用最多的应该是四种格式的文件,BIT、BIN、MCS和HEX。其实,bit文件用于调试,通过JTAG进行在线烧录调试,BIN和MCS用于固化,生成存储于flash的固化文件。对于HEX,可能很多人没有用过,但是与软件打过交道的人,应该会使用过,比如跟软件约定文件格式,自定义配置通过网络、PCIe接口方式进行配置数据的更新,当然,有些应用场景直接使用BIN文件或者MCS文件也可以用于在线升级。

1、文件格式差异

这几种配置数据文件格式的差异在哪里?

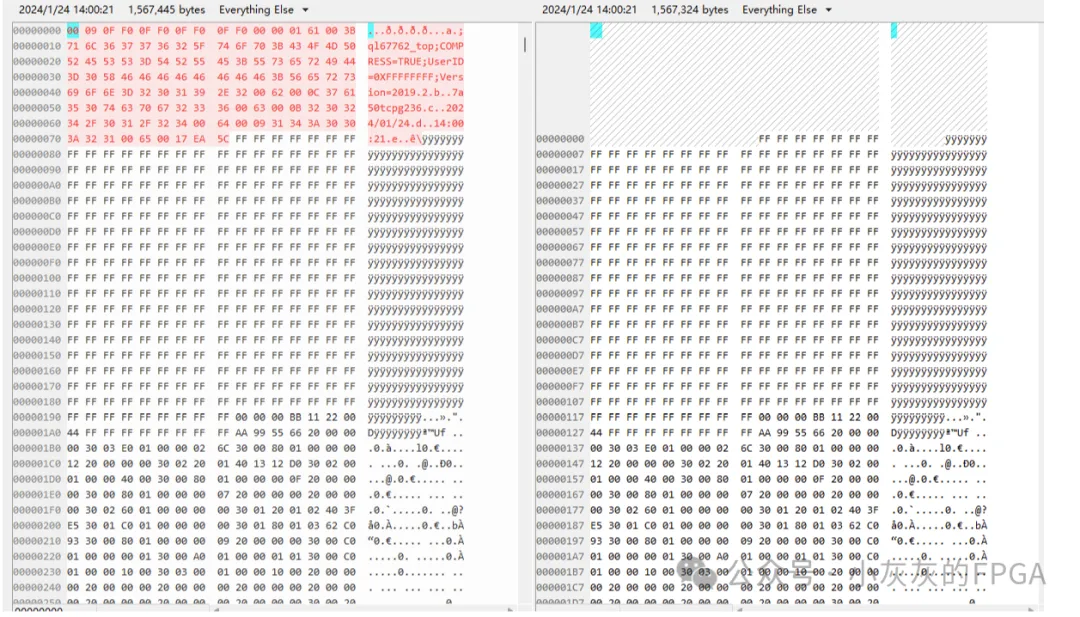

从上表中可以看出来,bit文件包含头信息,头信息里面包含了vivado的开发平台以及日期等等,下图中左侧为bit文件,右侧为BIN文件,没有头信息。

2、FPGA比特流内容

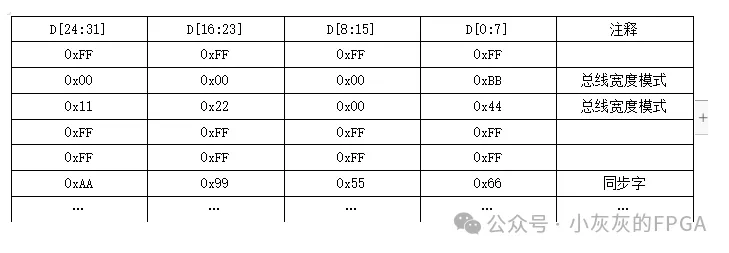

7系列FPGA比特流包括三个部分:总线宽度自动检测、同步字和FPGA配置。总线宽度自动检测模式插入在每个比特流的开始。它用于并行配置模式,以自动检测配置总线宽度。因为它出现在Sync字之前,串行配置模式会忽略它。总线宽度自动检测对大多数用户来说是透明的,因为Xilinx工具生成的所有配置位流(BIT或RBT文件)都包括总线宽度自动探测模式。如果模式引脚设置为主串行、从串行、JTAG或SPI模式,配置逻辑将忽略这些模式。

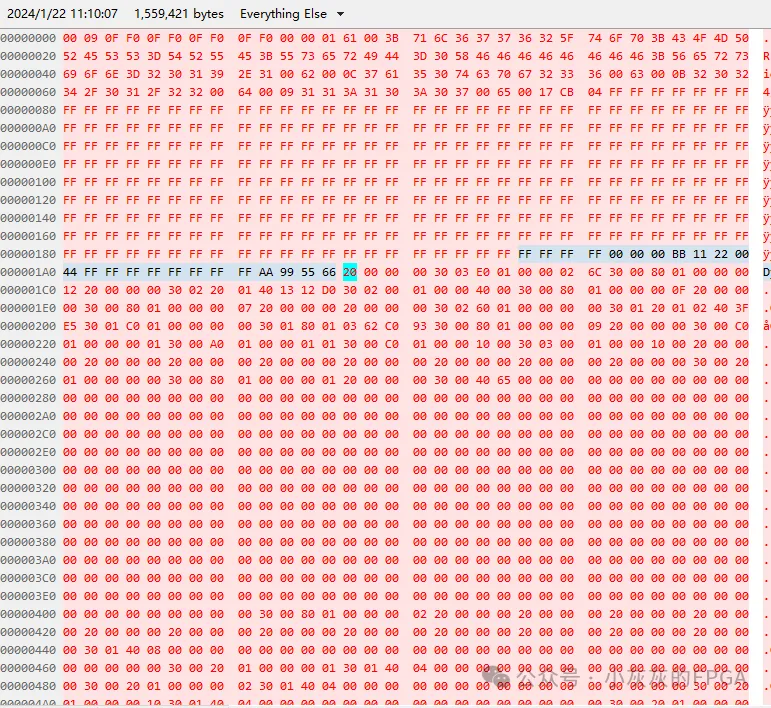

这个功能仅了解即可,从项目应用中来说,通常采用主SPI模式,但是生成的配置文件中这些内容一直存在。下图为一个bit文件,图中阴影部分就与上述中的总线宽度模式以及同步字等一一对应,同步字之后才是FPGA设计功能的配置内容。

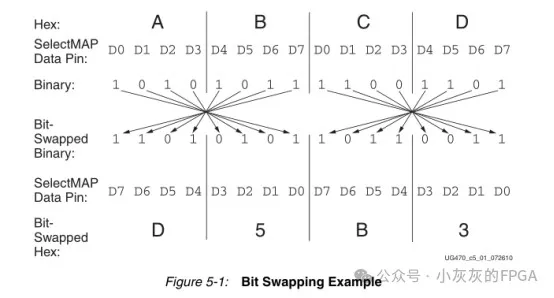

3、位交换

位交换是交换字节内的位。MCS PROM文件格式总是进行位交换,除非使用了SPI配置模式的PROMGen -spi选项或write_cfgmem -interface spi1|spi2|spi4选项。HEX文件格式可以进行位交换,也可以不进行位交换,这取决于用户的选项。比特流文件(BIT, RBT, BIN)从不进行位交换。HEX文件格式只包含配置数据。其他PROM文件格式包括不应该发送到FPGA的地址和校验和信息。地址和校验和信息被一些第三方设备编程人员使用,但没有被编程到PROM中。

需要注意的是:无论数据的方向如何,每个字节的MSB都将进入D0引脚:•在数据交换的版本中,进入D0的位是最右边的位•在非交换数据中,进入D0的位是最左边的位。

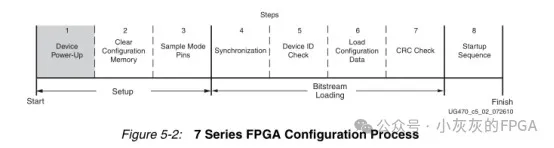

二、配置时序步骤

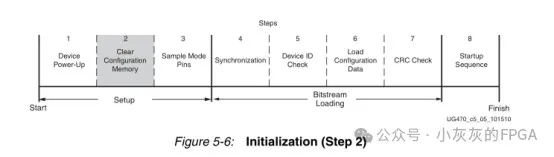

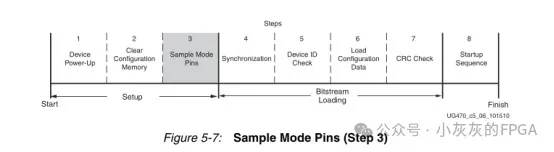

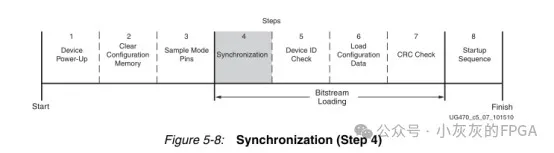

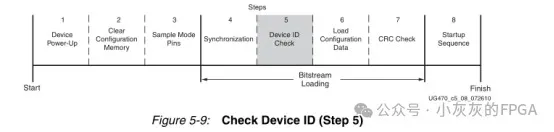

7系列FPGA的配置过程,通过三大设置过程,即8个小步骤来对模式引脚进行采样,从而确定配置模式,三大设置过程分别为:Setup、Bitstream Loading和Finish。

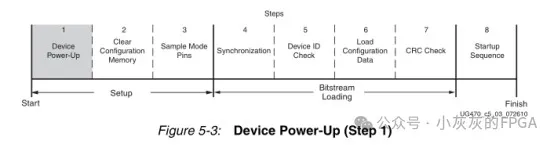

1、步骤一:设备通电

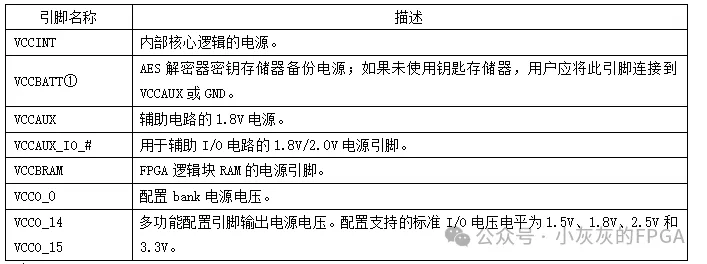

对于配置,7系列设备需要在VCCO_0, VCCAUX, VCCBRAM和VCCINT引脚上电。所有JTAG配置引脚都位于具有专用电压电源(VCCO_0)的单独专用组中。多功能引脚位于bank14和bank15。所有专用输入引脚工作在VCCO_0 LVCMOS电平。所有有源专用输出引脚在VCCO_0电压电平下工作,输出标准设置为LVCMOS, 12mA驱动,快速摆压率。对于所有使用多功能I/O的模式,必须将相关的VCCO_14或VCCO_15连接到合适的电压上,以匹配配置设备的I/O标准。引脚也是LVCMOS, 12mA驱动,配置时转换速度快。对于上电,VCCINT电源引脚必须提供1.0V或0.9V(对于-2L)源。在JTAG模式下配置7系列FPGA时,除了VCCO_0外,其他I/O电压电源都不需要上电。当选择使用多功能引脚(即Serial, Master BPI, SPI, SelectMAP)的配置模式时,还必须提供VCCO_14, VCCO_15或两者。

2、步骤二:清除配置内存

在设备上电、PROGRAM_B引脚脉冲为低之后、使用JTAG JPROGRAM指令或IPROG命令之后,或者在回退重试配置序列期间,配置内存都会被顺序清除。块RAM被重置到初始状态,触发器通过全局重置(GSR)的断言被重新初始化。在此期间,除了少数配置输出引脚外,通过使用全局三态(GTS)将I/ o置于高阻状态,并且如果PUDC_B低,将具有内部上拉。INIT_B在初始化时被内部驱动为低,在上电的情况下在TPOR(图5-4)后释放,在其他情况下为TPL。如果INIT_B引脚在外部保持低,设备在初始化过程中等待这个点,直到引脚被释放,并且满足TPOR或TPL延迟。

3、步骤三:采样模式引脚

当INIT_B引脚转换为高电平时,如果处于主模式,设备将对M[2:0]模式引脚进行采样并开始驱动CCLK。此时,设备开始在配置时钟的上升沿对配置数据输入引脚进行采样。对于BPI和SelectMAP模式,总线宽度最初为x8,状态寄存器反映了这一点。在总线宽度检测序列之后,状态寄存器被更新。仅在通过电源循环或PROGRAM_B的断言进行重新配置时,才再次对模式引脚进行采样。

4、步骤四:同步

对于BPI、Slave SelectMAP和Master SelectMAP模式,必须首先检测总线宽度(参见总线宽度自动检测)。总线宽度检测模式被从串行、主串行、SPI和JTAG模式忽略。然后,必须向配置逻辑发送一个特殊的32位同步字(0xAA9955566)。同步字提醒设备即将到来的配置数据,并将配置数据与内部配置逻辑对齐。

5、步骤五:检查设备ID

设备同步后,必须通过设备ID检查才能加载配置数据帧。这可以防止使用为不同设备格式化的比特流进行配置。如果在配置过程中发生ID错误,设备将尝试进行回退重新配置。

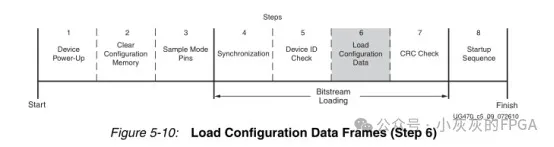

6、步骤六:加载配置数据帧

在加载同步字并检查设备ID之后,加载配置数据帧。

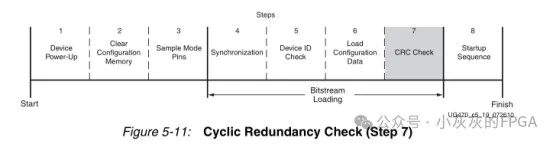

7、步骤七:冗余循环检查

7系列设备使用32位CRC校验。CRC校验被设计用于捕获传输配置比特流时的错误。当加载配置数据帧时,设备根据配置数据包计算循环冗余校验(CRC)值。在加载配置数据帧之后,配置比特流可以向设备发出校验CRC指令,随后是期望的CRC值。如果设备计算的CRC值与比特流中的预期CRC值不匹配,则设备将INIT_B拉低并中止配置。

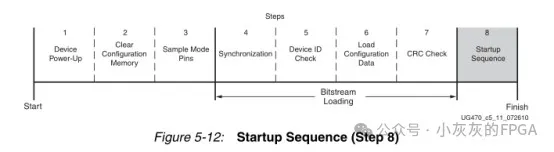

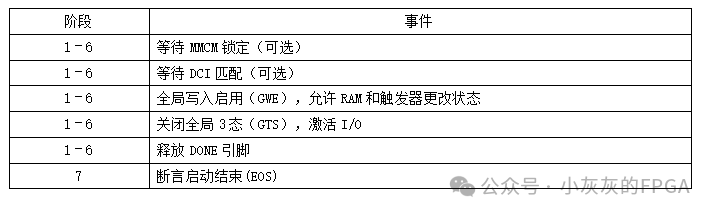

8、步骤八:启动

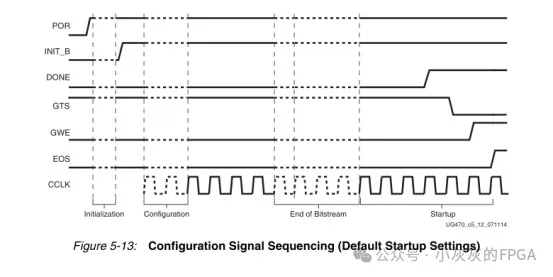

在加载配置帧之后,比特流指示设备进入启动序列。启动顺序由8相(0–7相)顺序状态机控制。

注明:本内容来源网络,不用于商业使用,禁止转载,如有侵权,请来信到邮箱:429562386ⓐqq.com 或联系本站客服处理,感谢配合!