时间:2025-03-08 来源:FPGA_UCY 关于我们 0

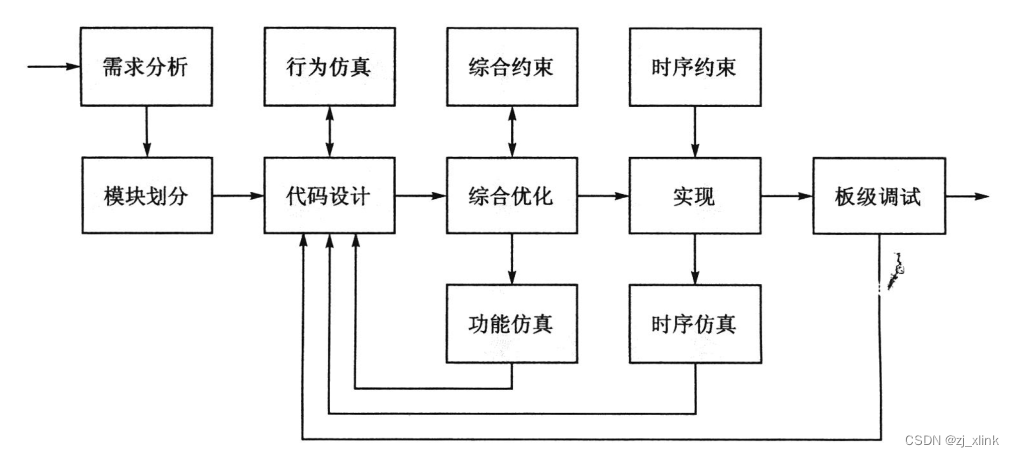

开发流程如下:

1、需求分析

首先明确用户需求,确定需要实现的功能,需要多少资源、I/O口的使用量,接口电平和系统功耗等,在此基础上进行FPGA选型。

2、模块设计

浩大的工程一般会有主设计师进行整体把握,进行模块划分,设计合理的架构,便于后期维护与升级。

3、设计输入

完成模块划分后,进行设计输入。主要有代码设计、原理图设计、SOPC设计三种方式,原理图设计局限于小规模设计或用于顶层设计,SOPC逐渐广泛起来,但代码设计依旧是目前主流的设计方法。

4、综合优化

完成设计输入后,需要进行综合,将较高层次的电路描述转化为较低层次的电路描述。通常使用综合工具将设计代码转换为与门、非门、RAM、触发器等基本逻辑单元相连的网表。

5、功能仿真

代码设计并综合后,需要进行功能仿真,此过程不涉及任何时序上的延时,只是验证各个模块的功能,通常此过程需要与代码设计进行反复的循环以满足设计要求。

6、时序约束与仿真

由于功能仿真不涉及任何时序延时,而实际的电路是有延时的,为保证整个系统的稳定运行,需要进行时序约束,分析系统各个部分的时序是否满足要求,并作相应的修改。

7、板级调试

板级调试即将系统运行在实际的硬件上,通常需要使用示波器、外部逻辑分析仪、在线逻辑分析仪等辅助工具来进行调试。