时间:2025-03-04 来源:FPGA_UCY 关于我们 0

3)全套实验源码+手册+视频下载地址:

第十七章 RS485串口通信实验

RS-485是针对UART串口的一种接口标准,它定义了串行通信系统中发送器和接收器的一系

列电气特性。相比于RS-232,RS-485标准的通信系统抗干扰能力较强,可实现长距离数据传输,

同时支持多个收发器连接到同一个通信网络中。因此,RS-485在工业控制领域以及有类似需求

的系统中得到了广泛的应用。

本章包括以下几个部分:

17.1 RS-485简介

17.2 实验任务

17.3 硬件设计

17.4 程序设计

17.5 下载验证

RS-485简介

在“串口通信实验”章节我们详细地介绍了UART串口通信以及RS-232接口标准。实际上,

除了RS-232之外,RS-422和RS-485也都是常用的串行通信接口标准,它们定义了接口不同的电

气特性,如RS-232是单端输入输出,而RS-422/485为差分输入输出等。

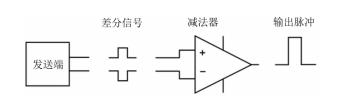

在介绍RS-485之前,我们先来了解一下串口通信过程中单端传输与差分传输的差别。单端

传输是指在发送或接收过程中,用信号线对地线的电压值来表示逻辑“0”和“1”。而差分传

输使用两根信号线来传输一路信号,这两根信号线上传输的信号幅值相等,相位相差180度(极

性相反),用它们的差值来表示逻辑“0”和“1”,如图 17.1.1所示。

图 17.1.1 差分传输方式

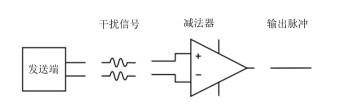

在传输过程中,当信号线上叠加了频率、幅值和相位都相同的干扰信号时(共模干扰),

对于单端传输而言,由于地线电位为0,则传输的信号就包含了干扰信号;而在差分传输方式

下,干扰可以通过两个信号线上电压的差值抵消,相当于抑制了共模干扰,如图 17.1.2所示。

因此相对于单端传输方式,差分传输大大提高了信号在传输过程中的抗干扰能力,但是需要多

余的信号线来实现信号传输。

图 17.1.2 差分传输抑制共模干扰

RS-232接口标准出现较早,信号采用负逻辑电平、单端传输方式工作。通过一根信号线发

送,一根信号线接收,加上一根地线,RS-232可实现全双工通信。由于单端传输方式抗干扰能

力差,导致RS-232标准通信距离短(小于15米),数据传输速率低等问题。另外RS-232仅支持

一对一通信,存在无法实现多个设备互联的缺点。

RS-422由RS-232发展而来,它是为弥补RS-232之不足而提出的。RS-422采用差分传输(又

称平衡传输)方式,将最大传输速率提高到;当传输速率在以下时,传输距离

可达1200米。由于采用差分传输方式,RS-422需要4根信号线来实现全双工通信,两根用于发

送、两根用于接收,一般会再加上一根地线。RS-422允许在一条传输总线上连接最多10个接收

器,从而实现单个设备发送,多个设备接收的功能。

为扩展应用范围,在RS-422基础上又制定了RS-485标准。RS-485同样采用差分传输方式,

但是RS-485只有2根信号线,由发送和接收共用,因此发送和接收不能同时进行,只能实现半

双工通信。RS-485增加了多点、双向通信能力,即允许多个发送器连接到同一条总线上,各设

备通过使能信号控制发送和接收过程。

实验任务

本节实验任务是使用两块开拓者开发板通过RS-485端口互联,由各自开发板上的四个按键

分别控制对方开发板上四个LED灯的亮灭。当按键按下时,对方开发板上对应的LED灯点亮;按

键释放时,对应的LED灯熄灭。

硬件设计

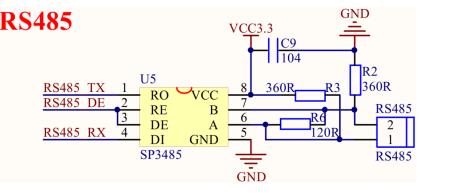

RS485串口部分的原理图如图 17.3.1所示。由于FPGA串口输入输出引脚为TTL电平,用3.3V

代表逻辑“1”,0V代表逻辑“0”;而RS-485电平标准采用差分信号的差值电压来代表逻辑“0”

和“1”。因此当FPGA与RS485接口标准的设备通信时,需要加电平转换芯片,实现RS485

电平与TTL电平的转换。

图 17.3.1 RS485串口原理图

由于RS-485为半双工通信方式,需要通过使能信号来控制发送和接收过程。在图 17.3.1

中,电平转换芯片的2号引脚为低电平接收使能,3号引脚为高电平发送使能。在这里我

们将两个引脚连接在一起,只需要通过一个信号即可控制收发过程:当为高

电平时,处于发送过程;当为低电平时,处于接收过程。

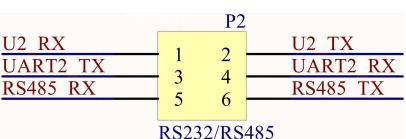

图 17.3.2 RS232/RS485选择接口

图 17.3.2为RS232/RS485的选择接口,由上图可知,芯片端口的和

并没有直接和FPGA的引脚相连接,而是连接到开发板的P2口,RS232串口和RS485串口

共用P2口的和,和是直接和FPGA的引脚相连接的,这样的

设计方式实现了有限IO的多种复用功能。因此,在做RS485串口通信实验时,需要使用杜邦线

或者跳帽将和连接在一起,和连接在一起。

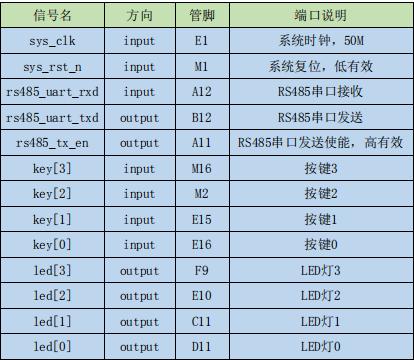

本实验中,各端口信号的管脚分配如下表所示:

表 17.3.1 RS485串口通信实验管脚分配

程序设计

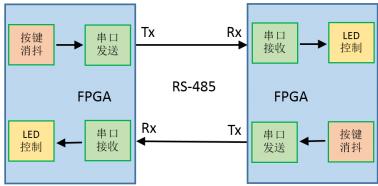

根据实验任务,我们可以大致规划出系统的控制流程:当检测到有按键按下或释放时,将

按键数据通过RS485串口发送出去;而当RS485串口接收到对方发送的按键数据时,根据接收到

的数据改变LED灯的显示状态。由此画出系统的功能框图如下所示:

图 17.4.1 RS485串口实验系统框图

由系统总体框图可知,FPGA部分包括五个模块,顶层模块()、接收模块

()、发送模块()、按键消抖模块()和LED灯控制模块

()。其中在顶层模块中完成对另外四个模块的例化。

由于RS-485只是对接口标准的定义,数据的传输仍然是按照UART串口通信协议进行。因此

我们可以直接调用“串口通信实验”中的串口发送和接收模块。在这里我们仍然设置数据位为

8位,停止位为1位,无校验位,波特率为。

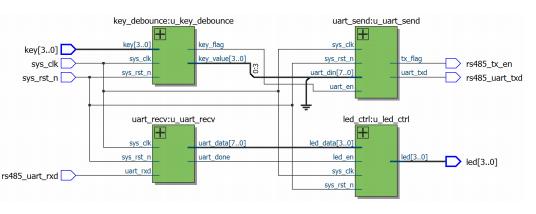

各模块端口及信号连接如图 17.4.2所示:

图 17.4.2 顶层模块原理图

为按键消抖模块,在检测到有按键按下或释放时对按键数据进行消抖处理,

在按键数据稳定后给出通知信号,并将数据由串口发送模块发送出去。

为串口接收模块,它负责接收对方发送的按键数据,并在一帧数据(8位)接收结束

后给出通知信号。当LED灯控制模块检测到该通知信号时,根据接收到的按

键数据改变板卡上LED灯的显示状态。

顶层模块的代码如下:

1 (

2 input , //外部50M时钟

3 input , //外部复位信号,低有效

5 input [3:0] key, //按键

6 [3:0] led, //led灯

7 //uart接口

8 input , //rs485串口接收端口

9 , //rs485串口发送端口

10 //rs485发送使能,高有效

11 );

12

13 //

14 = ; //定义系统时钟频率

15 = ; //定义串口波特率

16

17 //wire

18 wire ; //UART发送使能

19 wire ; //UART接收完毕信号

20 wire [7:0] ; //UART发送数据

21 wire [7:0] ; //UART接收数据

22 wire [3:0] ; //消抖后的按键数据

23

24 //*****************************************************

25 //** main code

26 //*****************************************************

27 = {4'd0,}; //将按键消抖后的值送到发送模块

28

29 #( //串口接收模块

30 . (), //设置系统时钟频率

31 . ()) //设置串口接收波特率

32 (

33 . (),

34 . (),

35

36 . (),

37 . (),

38 . ()

39 );

40

41 #( //串口发送模块

42 . (), //设置系统时钟频率

43 . ()) //设置串口发送波特率

44 (

45 . (),

46 . (),

47

48 . (),

49 . (),

50 . (),

51 . () //rs485串口发送使能,高有效

52 );

53

54 (

55 . (),

56 . (),

57

58 .key (key),

59 . (), //按键有效通知信号

60 . () //按键消抖后的数据

61 );

62

63 (

64 . (),

65 . (),

66

67 . (), //led控制使能

68 . ([3:0]), //led控制数据

69 .led (led)

70 );

71

72

顶层模块中主要完成对其余模块的例化,需要注意的是程序第27行:由于板卡上只有4个

按键,而串口通信过程中数据位为8位,因此需要将消抖后得到的4按键位数据高位补四个零,

然后再给到串口发送模块。同样,在将接收的按键数据用于LED灯控制时,仅将低四位有效位

赋值给LED灯控制模块,如第68行所示。

串口接收程序与“串口通信实验”章节中的接收模块完全相同,而串口发送程序有一点细

微的差异:将串口发送模块内部的“发送过程标志寄存器”作为输出端口引出,如代

码中第51行所示。由于在发送过程中为高电平,发送结束后拉低,因此可以将

其赋值给RS-485串口发送使能信号,用于控制串口通信的发送和接收过程。

信号通过FPGA管脚与芯片的DE和RE引脚相连,因此在串口发送过程中使能

进入发送状态,其他时间均处于接收状态。

有关串口收发过程更详细的介绍请大家参考“串口通信实验”,下面我们来介绍一下另外

两个模块:按键消抖模块和LED灯控制模块。

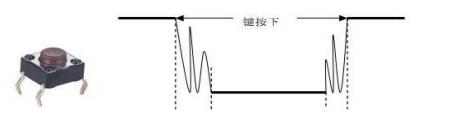

在机械按键按下和释放的过程中,由于机械触点的弹性作用,按键开关在闭合的瞬间不会

立即稳定地导通,在释放时也不是立刻就能完全断开。因此,在闭合及断开的瞬间均伴随有一

连串的抖动,如图 17.4.3所示。按键的抖动过程体现在数字电路中就是不断变化的高低电平,

为避免在抖动过程中采集到错误的按键状态,我们需要对按键数据进行消除抖动处理。

图 17.4.3 机械按键抖动过程

按键抖动的时间长短由按键的机械特性决定,一般为5ms~10ms,在抖动时间内按键状态

可能会不断的发生变化。由于按键的抖动过程持续时间较短,很快就趋于稳定状态。因此在按

键按下及释放之后,若按键能稳定在同一状态且持续时间达20ms,我们就认为抖动过程已经结

束,此时的采集的按键数据有效。

按键消抖模块的代码如下所示:

1 (

2 input , //外部50M时钟

3 input , //外部复位信号,低有效

5 input [3:0] key, //外部按键输入

7 reg , //按键数据有效信号

8 reg [3:0] //按键消抖后的数据

9 );

10

11 //reg

12 reg [31:0] ;

13 reg [ 3:0] ;

14

15 //*****************************************************

16 //** main code

17 //*****************************************************

18 @( or ) begin

19 if (!) begin

20