时间:2025-02-01 来源:FPGA_UCY 关于我们 0

关注、星标公众号,精彩内容每日送达

来源:网络素材FPGA开发流程 1.1 一般性的FPGA开发流程

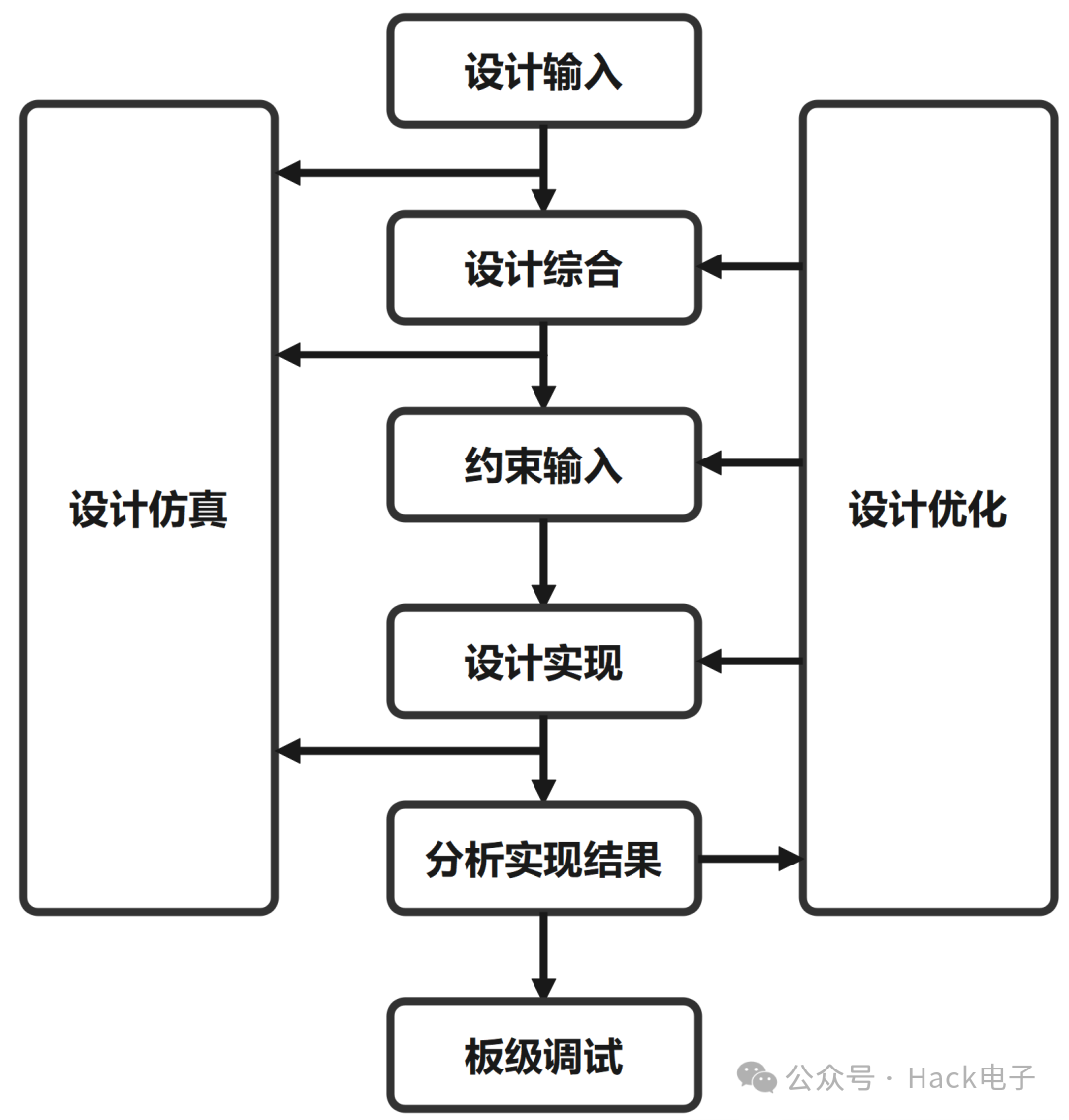

图1- 一般性FPGA开发流程

设计输入:创建FPGA工程,添加设计源文件,比如HDL文件、EDIF或NGC网表文件、原理图、IP核模块、嵌入式处> 理器以及数字信号处理器模块等。

设计综合: FPGA开发工具的综合引擎将编译整个设计,并将HDL源文件转译为特定结构的设计网表

约束输入:指定时序、布局布线或者其它的设计要求。如时序约束、I/O弓|脚约束和布局布线约束等

设计仿真:使用仿真I具对FPGA工程进行功能或时序验证。

设计实现:将逻辑设计进一步转译为可以被下载烧录到目标FPGA器件中的特定物理文件格式。

分析实现结果:对设计约束、器件资源占用率、实现结果以及功耗等设计性能进行分析

设计优化:分析当前设计结果,对设计源文件、编译属性或设计约束进行修改,然后重新综合、实现以达到设计最优化。FPGA的设计有很多迭代的过程。

板级调试:生成比特流并下载到开发板上,对FPGA器件进行板级的调试。FPGA有非常丰富的板级调试手段,比如在线逻辑分析仪可以直接查看FPGA内部引脚、接口、走线的信号变化,可以有效提升板级调试效率。

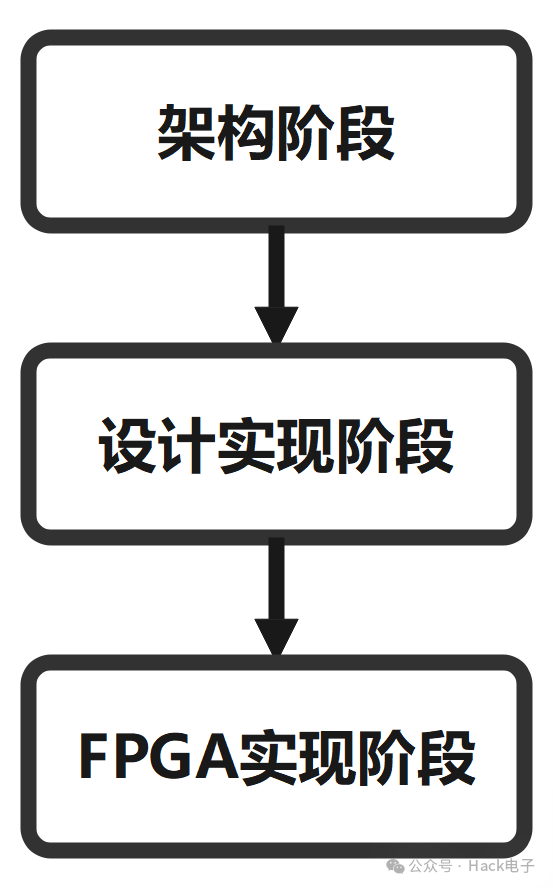

图1-2 简化的FPGA开发流程

概念阶段:或称架构阶段,完成项目前期的立项准备,如需求的定义和分析、各个设计模块的划分。

设计实现阶段:或称详细设计阶段,包括编写RTL代码、并对其进行初步的功能验证、逻辑综合和布局布线、时序验证。

FPGA器件实现阶段:除了器件烧录和板级调试外,也应该包括设计实现阶段的布局布线和时序验证,因为这两个步骤也都是和FPGA器件紧密相关的。

1.2 利用开发FPGA

就是用来进行FPGA开发的一个工具,可以编译硬件代码,完成上面所说的整个FPGA开发流程。市面上主流的FPGA开发工具只有两款,一个是芯片(被AMD收购)专用的 ,另一款则是芯片(被Intel收购)专用的 ,两者原理相同,但建议先熟练掌握一个工具而不是混着学。本教程选用正点原子达芬奇PRO开发板,搭载了的芯片,所以本教程都是用进行开发。

另外,集成了 HLS( High Level ) 工具,可以实现直接使用C、C++以及 C语言对的FPGA器件进行编程。用户无需手动创建RTL,通过高层次综合生成HDL级的IP核,从而加速IP创建。在某些使用语言描述异常复杂的场景中(如卷积神经网络),使用HLS将高级语言转化为对应的HDL级的IP核,就会非常方便。这种功能会在ZYNQ系列芯片的学习过程中进行介绍,本教程不涉及。

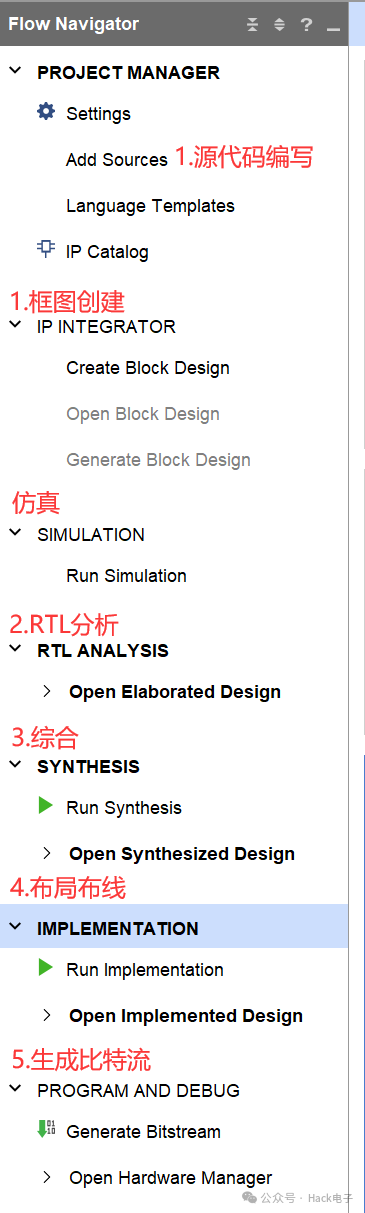

下面是左侧的导航窗格,上一节所述的FPGA开发流程都在这里完成:

图1-3 左侧导航窗格

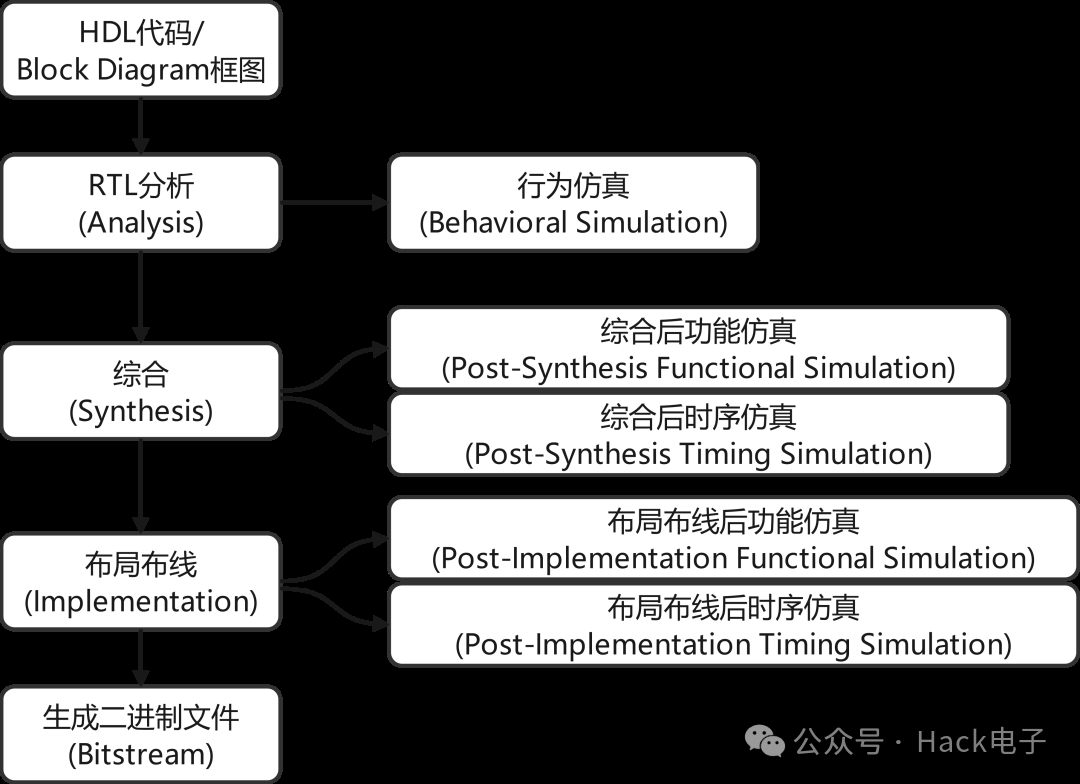

图1-4 基于的FPGA开发流程

创建源文件:用户有两种方式可以创建源文件,以描述电路结构与功能,分别是编写“HDL代码”、创建BD(框图,Block )。

RTL分析:将上述源文件转换为逻辑门电路。

此时可进行“行为仿真 ”。

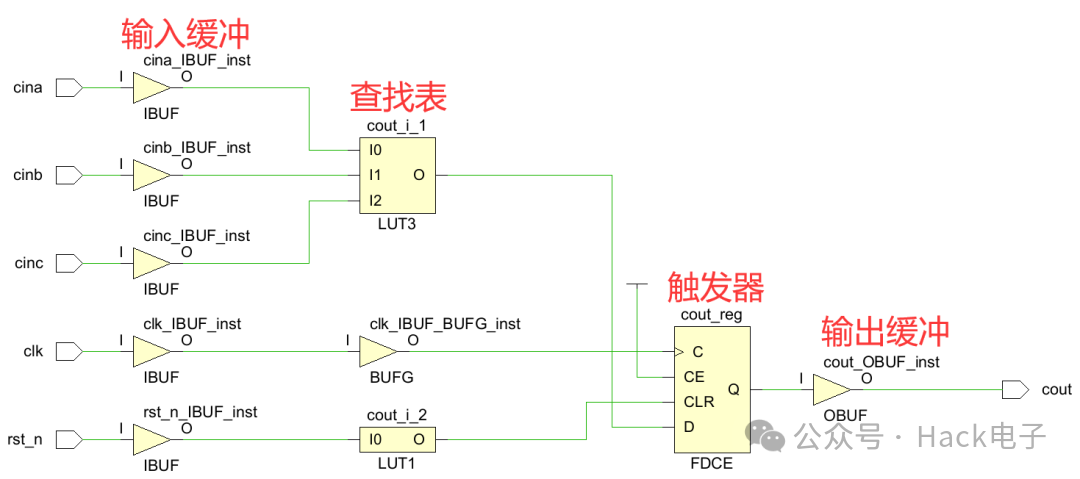

综合:将经过“RTL分析”后的门电路映射为FPGA器件内部的物理结构。所以“综合”电路中看不到任何的“门”。“综合”的结果是所使用的特定FPGA器件中实际存在着的物理结构,如“输入缓冲”、“查找表”、“触发器”和“输出缓冲”等。

此时可进行“综合后功能仿真”。

布局布线:需要用户指定时序、布局布线或者其它的设计要求,如时序约束、I/O引脚约束和布局布线约束等。会自动根据这些约束,将“综合”给出HDL代码与实际FPGA器件进行映射,物理视图与具体的芯片一致。

此时可以进行所有类型的仿真。

生成比特流、下载到板材上。

注:使用进行后续操作时,会自动检查前面的步骤是否已经完成,比如直接“综合”会自动先进行“RTL分析”、直接“生成比特流”则会自动进行整个过程,若有那个环节有错,会自动停止并给出提示。

在整个开发过程中,为了验证电路的正确性,还会进行仿真。从上面的示意图可以看到一共有5种仿真类型。主要分为行为仿真/功能仿真( / )、时序仿真( )两大类:

功能仿真也称为行为仿真,主旨在于验证电路的功能是否符合设计要求,其特点是不考虑电路门延迟与线延迟,主要是验证电路与理想情况是否一致。

时序仿真也称为布局布线后仿真,是指电路已经映射到特定的工艺环境以后,综合考虑电路的路径延迟与门延迟的影响,验证电路能否在一定时序条件下满足设计构想的过程,能较好地反映芯片的实际工作情况。但仿真耗时很长。

仿真是FPGA在板级调试前非常重要的验证手段。仿真可以在RTL分析前进行,但是为了提高仿真的有效性,需要先进行RTL分析、综合。另外,布局布线后也可以进行更精确的仿真,但是一般不做。在对时序要求不高的场景中,可以认为时钟的轻微延迟对电路基本没有影响,所以为了提高开发效率,一般只进行行为仿真( )。后续还有bug会使用ILA或VIO看波形异常,实在是找不出来问题,才会进行布局布线后时序仿真。

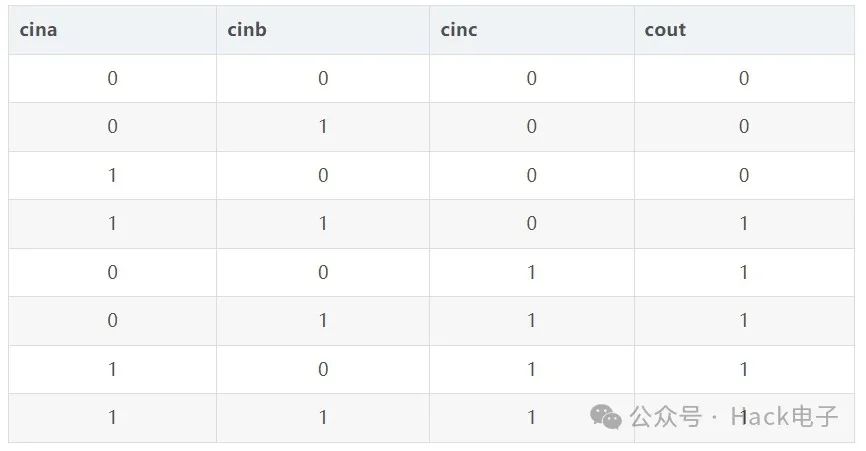

下面给出一个简单的开发实例:假如现在我们要开发一个电路,有三个输入信号A/B/C,输出为 AB+C,下面给出其真值表:

创建源文件,编写以下代码描述上述真值表所给出的逻辑功能。

module design_1(

clk,rst_p,

cina,cinb,cinc,

cout

);

//定义输入输出接口

input clk, rst_p; //时钟及复位信号

input cina, cinb, cinc; //输入的三个数据信号

output reg cout; //输出数据信号

//实现功能

always@(posedge clk or posedge rst_p)

if(rst_p)

cout <= 1'b0;

else

cout <= (cina & cinb) | cinc;

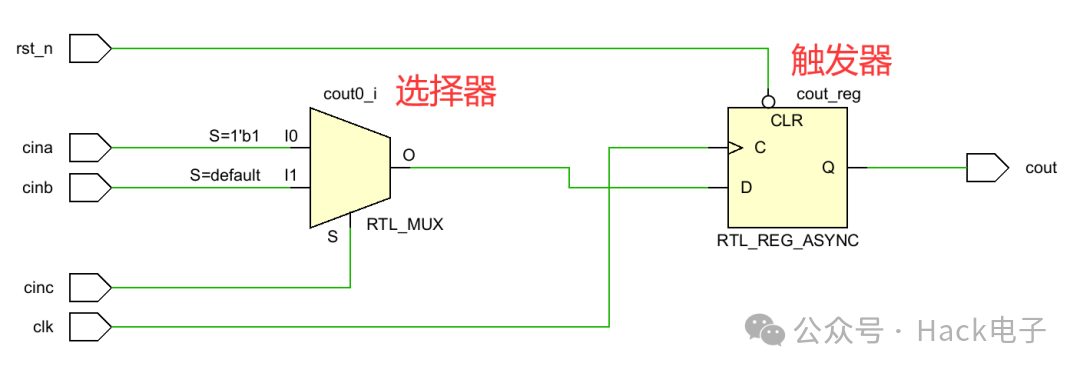

endmodule进行RTL分析(Run ),点击“Open ” → “”,即可看到RTL门级电路:

图1-5 【例】RTL门级电路

进行综合(Run ),将上面的门电路映射为FPGA芯片上实际的硬件电路,点击“Open ” → “”查看:

图1-12 【例】实际的硬件电路

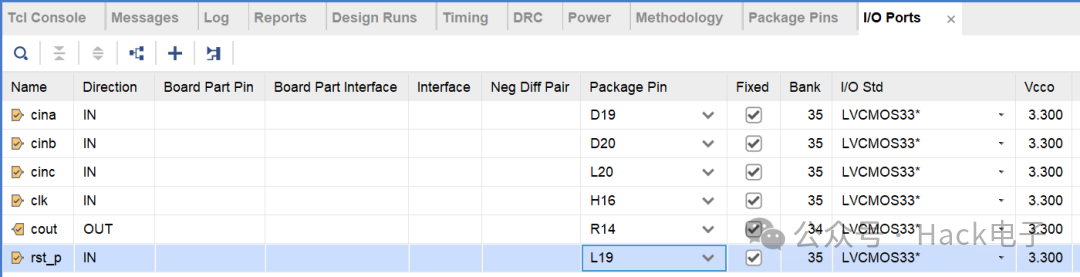

添加硬件约束(也就是引脚分配),通过查看PYNQ-Z2原理图可以发现系统时钟引脚为H16;四个按下为高电平的按键开关BTN3~BTN0的硬件端口依次为L19、L20、D20、D19;LED0端口为R14。设置BTN3为复位按键,BTN0~BTN2分别为cina/cinb/cinc,LED0为输出,于是分配硬件端口:

图1-6 【例】引脚约束

生成比特流,下载到开发板,就可以看到相应的实验现象了。

1.3 硬件调试与仿真(ILA核/VIO核)

那硬件开发的过程中,肯定也会出现各种各样的bug(实验现象与预期不符),在FPGA开发过程中,最主要的调试方式就是看各个主要信号的波形。本小小节就来介绍使用进行FPGA程序调试的思路。

1) 硬件异常检测

在进行程序调试前,首先要确定硬件本身没有问题。可以按照以下步骤进行:

下载一个验证好的例程,测试硬件是否能正常工作。

假如例程无法运行,排查接口连接、管脚分配。比如按照从电源到各个模块的顺序,测量各个模块的电压是否正常。

如果例程还是无法正常运行,交给硬件工程师/开发板卖家。

2) 行为仿真

确认硬件没有问题后,那么程序现象出问题就显然是软件程序的问题了。为了简单快捷,首先可以快速排查几个常见的错误:

检查 时钟、复位 是否接好。

检查每一个模块的接口是否正确。比如涉及到通信的问题,检查主控制和从控制器Slave是否建立的联系(两者之间的valid、ready信号)。

查看状态机的状态是否正常、查看数据是否有问题、查看触发条件是否有问题。(“状态机”后续会进行介绍)

注:任意查看“RTL分析”、“综合”、“布局布线”后的三种原理图,可以快速的查看电路连接状态。小技巧:

若此时还是没有发现问题,就需要编写仿真文件,来产生设计好的激励以驱动可能有问题的模块,这些激励包括时钟、复位、控制信号,另外也可以设计一些具有规律性的假数据来进行测试。仿真文件编写完毕后,再点击“运行”,就可以看到目标信号的仿真波形了。

3) ILA核与VIO核

一般通过上述“行为仿真”就能找出相应的bug了。但有些实验涉及到与外部芯片进行通信,导致不是所有的信号都是由FPGA内部控制,比如I2C通信读写、DDR3读写实验等。比较幸运时,可以找到该芯片对应的仿真代码,比如就有对应的仿真代码,可以直接在行为仿真中完全模拟出芯片信号的变化。但有些芯片可能没有对应的仿真代码;或者说有对应的仿真代码但实在是过于复杂,进行一次有效的行为仿真需要几十分钟,那这个时候就需要硬件电路的帮忙。换句话说,我想直接在有问题的硬件电路上,直接抓取信号看波形。

要想实现上面这个目的,首先想到的是使用示波器,但是示波器只能看到物理存在的接口。那想查看芯片内部信号的波形该怎么办呢?就需要使用内置的IP核:ILA核( Logic )、VIO核( Input/)。下面依次介绍。

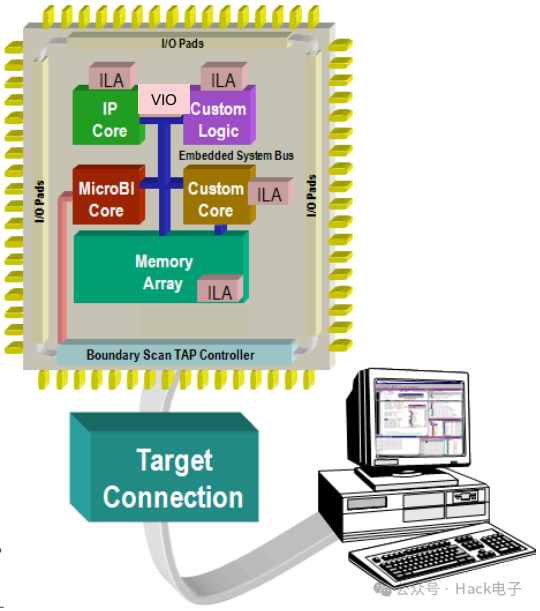

图1-7ILA/VIO 示意图

的LIA/VIO通过将Probe与相应的IP核相连,来监控逻辑内部信号和端口信号,最终将数据通过下载器(JTAG接口)传输到PC。简单来说,就是将数据发送到PC端(软件)进行显示。此外,VIO还可以接收电脑数据,用来驱动内部逻辑信号或提供触发信号。

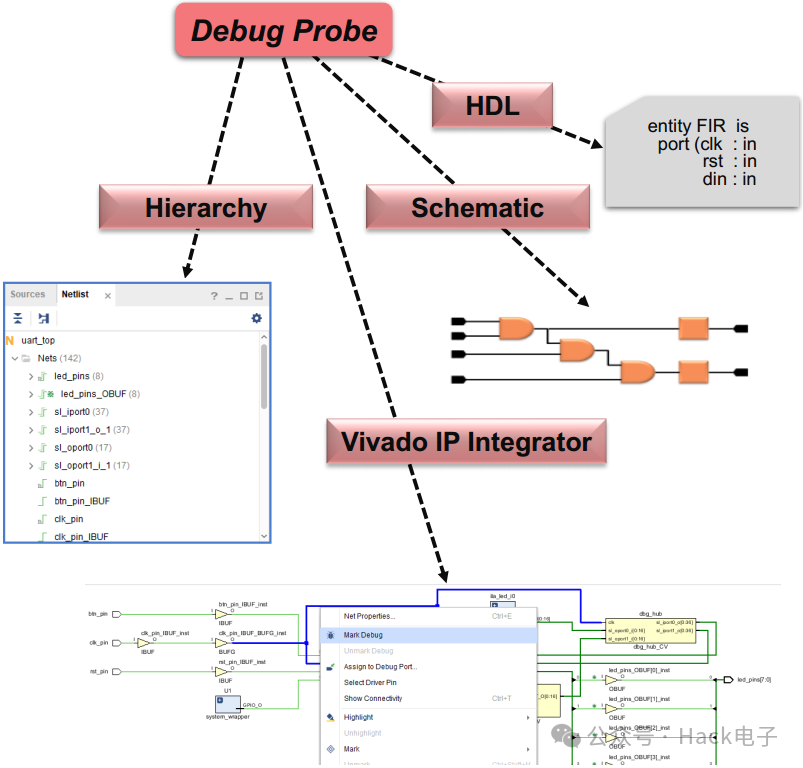

图1-8 添加ILA/VIO的方法

上图给出了添加ILA/VIO的方法:

HDL【常用】:生成ILA的IP核,然后在代码中进行例化。优点是方便,缺点是要修改代码。

信号列表()或原理图():对代码综合之后才能添加。优点是不用修改原代码,缺点是综合可能会优化掉待测信号(添加属性可以解决)。

IP (IP集成器):在IP 中添加信号,但是只有在添加硬核或软核才会用到。

注:添加成功后,下载比特流后会在软件窗口界面显示波形等设置。

总结:

ILA核:监控信号。可以将波形存储在ROM之中,但会消耗FPGA内部的逻辑资源和存储资源。

VIO核:监控和驱动信号。只能显示实时波形,但还可以通过电脑端手动更改程序的某些触发信号。

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索