时间:2024-07-25 来源:网络搜集 关于我们 0

所使用EDA软件:VIVADO2019.1.3

FPGA型号:xc7a35tcsg325-2

看完这篇文章你将收获以下内容:

理解XILINX中存储单元的结构

结合前面章节,理解CLB的整体结构

在数字电路中存储单元有两种,一种是触发器,一种是锁存器。它们两者最大的区别是

前者通过时钟沿到来改变存储的输出状态,后者是通过电平变换来改变存储的输出状态。

在FPGA中我们用的还是触发器居多,锁存器在很多情况下都是要避免的所以今天我主要还是讲触发器。

首先简单说明触发器特性(图1):在下一次时钟沿来临前,输出Q保持不变。当有时钟沿触发时,将输入D的电平转移到输出Q。

图1:触发器示意图

这里的电平转移指的是当输入高过一定阈值,输出就会输为高电平。输入低过一定阈值,输出就会输为低电平。讲人话,拿3.3VCMOS电平转移来说,当输入为2.1V(高过高电平阈值2.0V),输出就约等于3.3V。当输入为0.6V时(低过输入低电平阈值0.7V),输出就约等于0V。

然而我在前面一直说的用LUT做成的移位寄存器转移的是电荷,转移电荷就是输入时2.1V输出就2.1V,输入0.6V输出就是0.6V。所以出现亚稳态(电平在高低之间),用LUT做出的移位寄存器会打拍的话无法降低亚稳态的影响,只会让它一直传递下去。

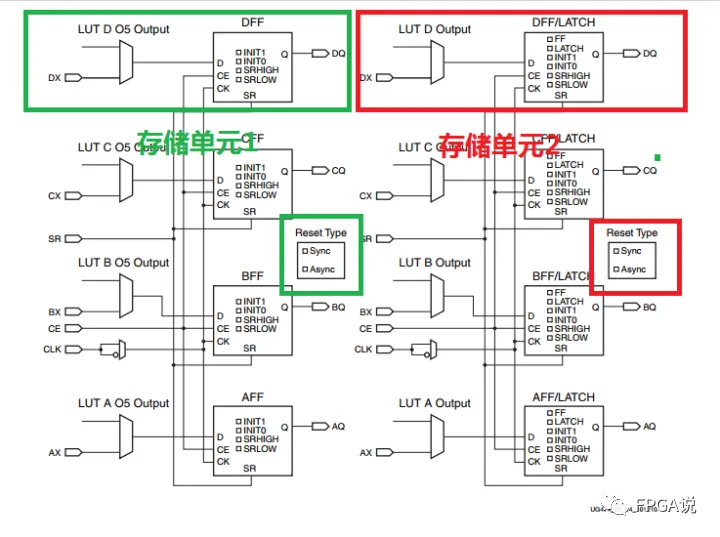

XILINX 7系中的存储单元结构(图2),它主要分为两种,我们帮他们起个名字,在图2中绿色大框内的我们叫存储单元1,在图2红色大框内的我们把它叫做存储单元2。

图2:XILINX 7系存储单元结构

存储单元1和存储单元2,有以下几个异同点。

相同点:

他们都具有数据输入端(D),时钟使能端(CE),时钟输入端(CK),以及复位端(SR)。

它们都能通过配置INIT1 INIT0来将上电复位或全局复位后的初始电平配置为高或者低(这里用的是FPGA中的全局复位管脚,非用户自定义那个,属异步复位)。

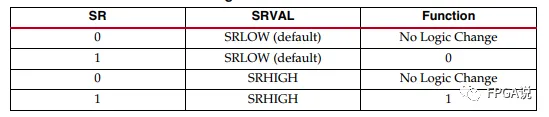

它们都能通过配置SRHIGH SRLOW 来控制用户复位后的的电平,与输入SR的关系如(图3)所示,从中我们还可以看到SR都是高电平有效的,这也是为啥XILINX 7系推荐高电平复位,低电平复位的话再前面还要插个LUT做反相器而造成浪费资源。(这里的用户复位通常指的是普通IO复位,如自定义用户按键复位)

在同一SLICE中,同一类型的存储单元的用户复位均可配置为异步或者同步复位(图2中绿色小框与红色小框分别配置存储单元1与存储单元2的可选择的复位类型)。

图3:SR与SRLOW SRHIGH(SRVAL)的关系

下面我们通过个简单的例子(例1)来告诉加深大家对INIT0,INIT1,SRLOW,SRHIGH的印象。

我们初始化 reg[7:0]r_data_tmp=8b0 时就是为了配置INIT0(INIT1)

在always语句中的 r_data_tmp<=8b0时就是为了配置SRLOW(INIT2)

o_data

);reg[7:0]r_data_tmp=8b0;//这里将会8个存储单元配置为INIT0 ,如果改成8b1111_1111则配置成INIT1always@(posedge clk)beginif(rst) r_data_tmp<=8b0;//这里将会8个存储单元配置为SRLOW ,如果改成8b1111_1111则配置成SRHIGHelse r_data_tmp<=i_data_1&i_data_2;endassign o_data=r_data_tmp;endmodule不同点:

存储单元1只能做触发器,而存储单元2既可做触发器又可以做锁存器。

存储单元1只能由外部旁路输入(不仅过LUT直接连到存储单元)以及所在行的LUT6的O5输出作为数据输入。存储单元2除了有存储单元1的特性以外,还可以由所在行的LUT6的O6输出、MUX7/MUX8的输出、进位链的输出作为输入。

注意事项:

存储单元的配置(同步,异步,复位后初始值等)确定后是无法通过外部输入无法修改的。

存储单元的数据输入通道也是无法中途修改的,因为它前面的MUX是没有数据选择端的,FPGA在运行时,这个MUX由哪一条通道作为输入是确认并且无法更改的。举个例子:存储单元2的输入为LUT的输出就一直为LUT的输出,无法改为外面的旁路输入或者进位链的输出作为输入。

接下来我们来总结一下前面几章有关CLB的内容。

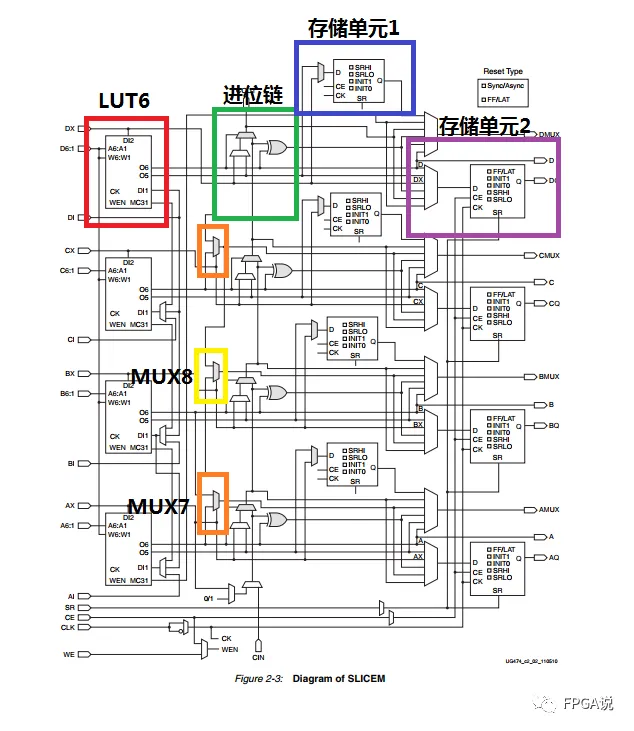

先祭出一开始让我们看到脑阔疼的SLICE的架构图(图4)。我们可以将它分为四行,每一行的内容都是相同的。LUT6->进位链->存储单元1/存储单元2

图4 XILINX 7系中SLICEM的架构图(SLICEL类似,只不过它的LUT6不具备读写功能)

蓝框和紫框分别是存储单元1,存储单元2。它们是时序电路中不可或缺的一部分,我们在verilog中每1位的reg几乎都会用到1个存储单元。这里存储单元的输入取决于它们前面的那个MUX。存储单元1有2种输入方式它前面的MUX就有2个数据输入端,存储单元2有5种输入方式,它前面的MUX就有5个数据输入端。

红框部分的LUT6,它内部由两个LUT5和1个MUX组成。1个LUT6可以实现6位输入1位输出的逻辑运算,也可以实现2个相同的5位输入2位输出的逻辑运算,还可以做MUX4_1。在SLICEM中的LUT6还可以做DRAM、移位寄存器实现数据读写,移位输出的功能。详细内容请参照前面的LUT、DRAM章节。

FPGA从入门到精通(2)-LUT

FPGA说,公众号:FPGA说FPGA从入门到精通(2) - LUT

FPGA从入门到精通(3)-DRAM

FPGA说,公众号:FPGA说FPGA从入门到精通(3) - DRAM

橙框、黄框中的MUXF7、MUXF8是为了将LUT拼接起来实现更大数据深度的LUT,DRAM或者移位寄存器(MUX不会增加数据宽度哦,小伙伴们要注意!!!),详细内容请参照前面MUX的内容。

FPGA从入门到精通(4)-MUX

FPGA说,公众号:FPGA说FPGA从入门到精通(4) - MUX

绿框中的进位链主要是为了实现多位加法器的功能,它的最大长度(加法器的位宽)取决当前区域的列高。详细内容请参照前面的进位链的内容。

FPGA从入门到精通(5)-进位链

FPGA说,公众号:FPGA说FPGA从入门到精通(5) - 进位链

接近输出端口的MUX(AMUX BMUX CMUX DMUX作为输出那个),它的特性其实是和存储单元2前面的那个MUX差不多的。仔细观察可以看到同一行的两种MUX 有5个端口的输入都是连在一起的,只不过一个是直接输出,另一个是打一拍再输出。剩下的1个端口,对于第一种MUX它是接存储单元1的输入的,对于第二种MUX它是直接接外部旁路输入的。(注意:两种MUX是没有数据选择端的,因此FPGA在运行时,由哪一条通道作为输入是确认并且无法更改的)

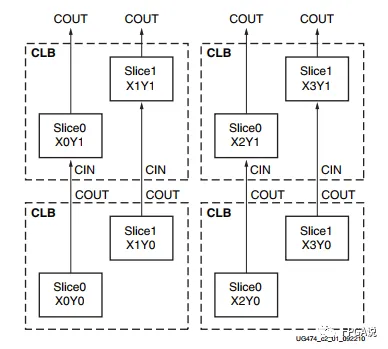

下面是SLICE在CLB中的排列(图5)

图5:SLICE在CLB中的排列

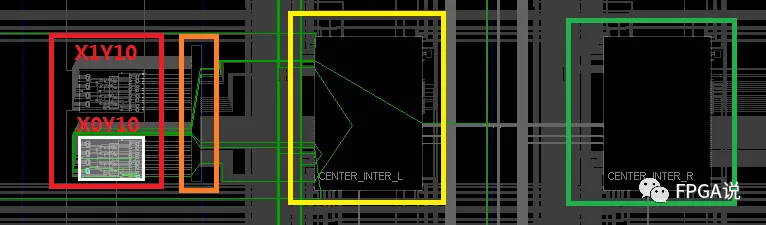

我们可以看到,一个CLB中有两个SLICE。分别是在CLB的左下角和右上角,上一级SLICE进位链的输出是连到同一列中下一级SLICE的进位链的输入。那么SLICE和SLICE之间除了进位之外是怎么互联的呢?我们通过看一下例1布局布线后的的情况(图6)对其有个简单的认识。由于EDA工具布局布线策略的问题,没把2个8位的输入都布在同一CLB内。当然这可以通过手动布局来更改,偷偷懒就不讲怎么实现啦。

图6:例1布局布线后的视图

红框内为同一CLB内的两个SLICE,虽然视图上他们是同一列,实际在FPGA是错开的,看X坐标就知道。橙色框是同一CLB内的快速互联(如果在同1CLB 就用它直连)。黄框 ,绿框内的互联单元我们把他当成为了把线连到更远处的“中继”,更多布局布线相关内容我会在后面讲约束的时候会提到。

好的今天的内容就到这里,后面的话我会举个例子来给大家展现压榨单个CLB的快感,谢谢!

我的公众号:FPGA说