本题库会更新硬件工程师笔试面试各个模块。从基本元器件开始,后面更新模电数电,电源,运放,PCB等各方面的设计知识,供相关行业笔试面试参考用。

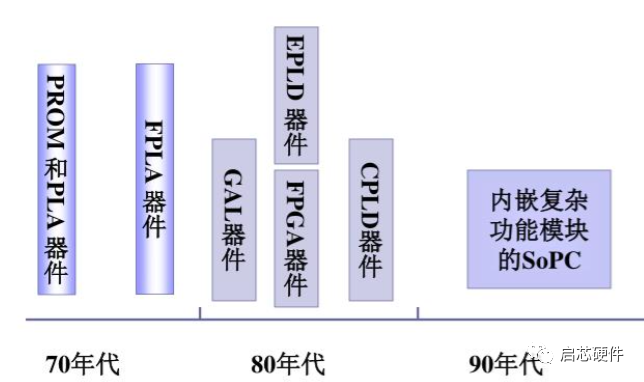

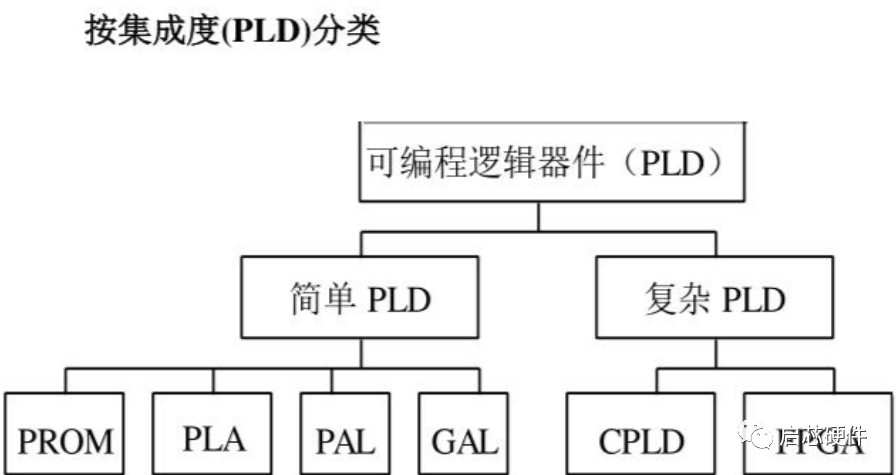

1、你所知道的可编程逻辑器件有哪些? 答:ROM(只读存储器)、PLA(可编程逻辑阵列)、FPLA(现场可编程逻辑阵列)、PAL(可编程阵列逻辑)GAL(通用阵列逻辑),EPLD(可擦除的可编程逻辑器件)、 FPGA(现场可编程门阵列)、CPLD(复杂可编程逻辑器件)等 ,其中 ROM、FPLA、 PAL、GAL、EPLD 是出现较早的可编程逻辑器件,而 FPGA 和 CPLD 是当今最 流行的两类可编程逻辑器件。FPGA 是基于查找表结构的,而 CPLD 是基于乘积 项结构的。可编程逻辑器件的演进:1)可编程逻辑阵列(PLA): PLA是早期可编程逻辑器件的一种。它允许用户编程任意的布尔逻辑方程,从而实现复杂的数字电路功能。PLA的主要优势在于其灵活性,但缺点由于它的结构相对复杂,成本较高。2)可编程阵列逻辑器件(PAL): 为了简化PLA并减小成本,可编程阵列逻辑器件应运而生。PAL具有一组可编程的与门和可编程的或门,使得用户能够灵活地定义逻辑功能。PAL的优势是提供了一种在门级别上实现逻辑的经济有效方法。3)复杂可编程逻辑器件(CPLD): CPLD是在PAL基础上发展起来的一种更复杂的可编程逻辑器件。它包含多个可编程逻辑块和连接资源,使得它更适用于实现较大规模的数字电路。CPLD通常具有更灵活的架构,使得用户可以实现更复杂的逻辑功能。4)现场可编程门阵列(FPGA): FPGA是可编程逻辑器件的最新发展阶段。它采用了现场可编程的门阵列结构,允许用户在现场(实际使用的地方)进行配置。FPGA在灵活性和性能之间取得了良好的平衡,使得它成为实现数字逻辑功能的重要工具。FPGA可以在运行时重新编程,支持广泛的应用,包括数字信号处理、通信、图像处理、网络加速等领域。

1、你所知道的可编程逻辑器件有哪些? 答:ROM(只读存储器)、PLA(可编程逻辑阵列)、FPLA(现场可编程逻辑阵列)、PAL(可编程阵列逻辑)GAL(通用阵列逻辑),EPLD(可擦除的可编程逻辑器件)、 FPGA(现场可编程门阵列)、CPLD(复杂可编程逻辑器件)等 ,其中 ROM、FPLA、 PAL、GAL、EPLD 是出现较早的可编程逻辑器件,而 FPGA 和 CPLD 是当今最 流行的两类可编程逻辑器件。FPGA 是基于查找表结构的,而 CPLD 是基于乘积 项结构的。可编程逻辑器件的演进:1)可编程逻辑阵列(PLA): PLA是早期可编程逻辑器件的一种。它允许用户编程任意的布尔逻辑方程,从而实现复杂的数字电路功能。PLA的主要优势在于其灵活性,但缺点由于它的结构相对复杂,成本较高。2)可编程阵列逻辑器件(PAL): 为了简化PLA并减小成本,可编程阵列逻辑器件应运而生。PAL具有一组可编程的与门和可编程的或门,使得用户能够灵活地定义逻辑功能。PAL的优势是提供了一种在门级别上实现逻辑的经济有效方法。3)复杂可编程逻辑器件(CPLD): CPLD是在PAL基础上发展起来的一种更复杂的可编程逻辑器件。它包含多个可编程逻辑块和连接资源,使得它更适用于实现较大规模的数字电路。CPLD通常具有更灵活的架构,使得用户可以实现更复杂的逻辑功能。4)现场可编程门阵列(FPGA): FPGA是可编程逻辑器件的最新发展阶段。它采用了现场可编程的门阵列结构,允许用户在现场(实际使用的地方)进行配置。FPGA在灵活性和性能之间取得了良好的平衡,使得它成为实现数字逻辑功能的重要工具。FPGA可以在运行时重新编程,支持广泛的应用,包括数字信号处理、通信、图像处理、网络加速等领域。  2、用 VHDL 或 VERILOG、ABLE 描述 8 位 D 触发器逻辑3、FPGA和ASIC的概念,他们的区别。(未知) 答案:FPGA是可编程ASIC。 ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。与 门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点。4、FPGA和ASIC的概念,他们的区别。(未知) 答案:FPGA是可编程ASIC。ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点。 5、什么是同步逻辑和异步逻辑?同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。6、如何解决亚稳态。答:亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在亚稳态期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。解决方法主要有:(1)降低系统时钟;(2)用反应更快的FF;(3)引入同步机制,防止亚稳态传播;(4)改善时钟质量,用边沿变化快速的时钟信号;(5)使用工艺好、时钟周期裕量大的器件。7、什么是同步逻辑和异步逻辑? 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 电路设计可分类为同步电路和异步电路设计。同步电路利用时钟脉冲使其子系统同步运作,而异步电路不使用时钟脉冲做同步,其子系统是使用特殊的“开始”和“完成”信号使之同步。由于异步电路具有下列优点--无时钟歪斜问题、低电源消耗、平均效能而非最差效能、模块性、可组合和可复用性--因此近年来对异步电路研究增加快速,论文发表数以倍增,而Intel Pentium 4处理器设计,也开始采用异步电路设计。 异步电路主要是组合逻辑电路,用于产生地址译码器、FIFO或RAM的读写控制信号脉冲,其逻辑输出与任何时钟信号都没有关系,译码输出产生的毛刺通常是可以监控的。同步电路是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路,其所有操作都是在严格的时钟控制下完成的。这些时序电路共享同一个时钟CLK,而所有的状态变化都是在时钟的上升沿(或下降沿)完成的。 7、解释setup time和hold time的定义和在时钟信号延迟时的变化。(未知) 8、解释setup和hold time violation,画图说明,并说明解决办法。 Setup/hold time是测试芯片对输入信号和时钟信号之间的时间要求。建立时间是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间。输入信号应提前时钟上升沿(如上升沿有效)T时间到达芯片,这个T就是建立时间-Setuptime.如不满足setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器。保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间。如果hold time不够,数据同样不能被打入触发器。 建立时间(Setup Time)和保持时间(Hold time)。建立时间是指在时钟边沿前,数据信号需要保持不变的时间。保持时间是指时钟跳变边沿后数据信号需要保持不变的时间。如果不满足建立和保持时间的话,那么DFF将不能正确地采样到数据,将会出现 metastability的情况。如果数据信号在时钟沿触发前后持续的时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量。 9、请用HDL描述四位的全加法器、5分频电路。10、用VERILOG或VHDL写一段代码,实现10进制计数器。(未知) 11、用VERILOG或VHDL写一段代码,实现消除一个glitch。(未知)

2、用 VHDL 或 VERILOG、ABLE 描述 8 位 D 触发器逻辑3、FPGA和ASIC的概念,他们的区别。(未知) 答案:FPGA是可编程ASIC。 ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。与 门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点。4、FPGA和ASIC的概念,他们的区别。(未知) 答案:FPGA是可编程ASIC。ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点。 5、什么是同步逻辑和异步逻辑?同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。6、如何解决亚稳态。答:亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在亚稳态期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。解决方法主要有:(1)降低系统时钟;(2)用反应更快的FF;(3)引入同步机制,防止亚稳态传播;(4)改善时钟质量,用边沿变化快速的时钟信号;(5)使用工艺好、时钟周期裕量大的器件。7、什么是同步逻辑和异步逻辑? 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 电路设计可分类为同步电路和异步电路设计。同步电路利用时钟脉冲使其子系统同步运作,而异步电路不使用时钟脉冲做同步,其子系统是使用特殊的“开始”和“完成”信号使之同步。由于异步电路具有下列优点--无时钟歪斜问题、低电源消耗、平均效能而非最差效能、模块性、可组合和可复用性--因此近年来对异步电路研究增加快速,论文发表数以倍增,而Intel Pentium 4处理器设计,也开始采用异步电路设计。 异步电路主要是组合逻辑电路,用于产生地址译码器、FIFO或RAM的读写控制信号脉冲,其逻辑输出与任何时钟信号都没有关系,译码输出产生的毛刺通常是可以监控的。同步电路是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路,其所有操作都是在严格的时钟控制下完成的。这些时序电路共享同一个时钟CLK,而所有的状态变化都是在时钟的上升沿(或下降沿)完成的。 7、解释setup time和hold time的定义和在时钟信号延迟时的变化。(未知) 8、解释setup和hold time violation,画图说明,并说明解决办法。 Setup/hold time是测试芯片对输入信号和时钟信号之间的时间要求。建立时间是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间。输入信号应提前时钟上升沿(如上升沿有效)T时间到达芯片,这个T就是建立时间-Setuptime.如不满足setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器。保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间。如果hold time不够,数据同样不能被打入触发器。 建立时间(Setup Time)和保持时间(Hold time)。建立时间是指在时钟边沿前,数据信号需要保持不变的时间。保持时间是指时钟跳变边沿后数据信号需要保持不变的时间。如果不满足建立和保持时间的话,那么DFF将不能正确地采样到数据,将会出现 metastability的情况。如果数据信号在时钟沿触发前后持续的时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量。 9、请用HDL描述四位的全加法器、5分频电路。10、用VERILOG或VHDL写一段代码,实现10进制计数器。(未知) 11、用VERILOG或VHDL写一段代码,实现消除一个glitch。(未知)

注明:本内容来源网络,不用于商业使用,禁止转载,如有侵权,请来信到邮箱:429562386ⓐqq.com 或联系本站客服处理,感谢配合!